XiaoMi-AI文件搜索系统

World File Search System赛车手:使用电阻内存

为了打击主要存储器和CPU之间移动数据的高能量成本,最近的作品提出了执行加工记忆(PUM)的工作,这是一种记忆中的一种处理,其中在现场进行数据操作(即,在存储单元格在持有数据的存储单元上)。几种常见和新兴的记忆技术提供了通过互连单元相互作用来执行比尔原始功能的能力,从而消除了对多个常见操作使用离散的CMOS计算单元的需求。最近的PUM架构扩展了这些布尔原始图,以使用内存执行比特系列的组合。不幸的是,基础内存设备的几个实际局限性限制了新兴内存阵列的大小,这阻碍了传统的位式计算方法的能力,除了大量的能源节省外,还可以提供高性能。在本文中,我们提出了赛车手,这是一个具有成本效益的PUM档案馆,可使用少量的电阻性记忆提供高性能和大量节省的能源。Racer利用了一个比特的上流执行模型,该模型可以在W小图块上管道位的w-bit计算。我们完全设计有效的控制和外围电路,它们的区域可以在不牺牲记忆密度的情况下在小记忆砖上摊销,我们为Racer提出了ISA抽象,以允许简单的程序/编译器集成。We evaluate an implementation of RACER using NOR- capable ReRAM cells across a range of microbenchmarks extracted from data-intensive applications, and find that RACER provides 107 × , 12 × , and 7 × the performance of a 16-core CPU, a 2304-shader- core GPU, and a state-of-the-art in-SRAM compute substrate, re- spectively, with energy savings of 189 × , 17 × ,和1.3×。

关于在广告中使用代言和推荐的指南

示例 4:一家汽车轮胎制造商聘请了一位知名的专业赛车手在电视广告中传递其广告信息。在这些广告中,赛车手谈到了轮胎的平稳驾驶、强度和长寿命。即使该信息没有明确声明为赛车手的个人观点,它仍然可能构成对轮胎的认可。许多消费者会认识到这个人主要是赛车手,而不仅仅是广告商的发言人或播音员。因此,他们很可能认为,除非赛车手真正相信自己所说的话,并拥有足够的个人知识来形成这种信念,否则他不会为汽车产品代言。因此,他们会认为广告信息反映了赛车手的个人观点。将潜在观点归因于赛车手使广告符合本部分中对认可的定义。

赛车手:认识论风险敏感的RL可以通过更少的撞车事故进行快速驾驶

摘要 - 强化学习为机器人控制提供了一个吸引人的框架,因为它仅通过现实世界的互动才能纯粹学习表达政策。但是,这需要解决现实世界的约束并避免在训练过程中造成灾难性失败,这可能会严重阻碍学习进步和最终政策的表现。在许多机器人设置中,这相当于避免某些“不安全”状态。高速越野驾驶任务代表了对此问题的特别挑战性的实例化:高回报策略应尽可能积极地驱动驱动力,通常需要接近“安全”状态集的边缘,因此在该方法上承担特定的负担,以避免频繁失败。既学习高表现的政策,又避免过度失败,我们提出了一个增强学习框架,将对风险敏感的控制与自适应动作空间课程相结合。此外,我们表明我们的风险敏感目标会自动避免配备认知不确定性的估计量。我们在小规模的拉力赛上实施了算法,并表明它能够为现实世界中的越野驾驶任务学习高速政策。我们表明,我们的方法大大减少了培训过程中的安全违规数量,实际上导致在驾驶和非驾驶模拟环境中都具有类似挑战的驾驶和非驾驶模拟环境中的绩效策略。

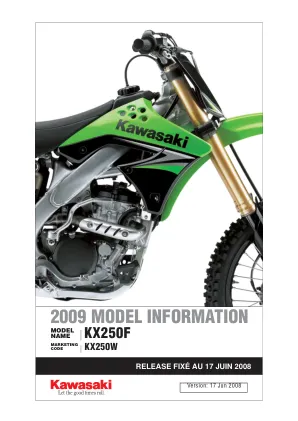

2009 款车型信息 - Mototribu

KX250F 基础套件为经验丰富的赛车手提供了一个绝佳的平台,帮助他们在顶级比赛中获胜。高刚性铝制框架、悬挂组件和设置的设计专注于提供卓越的高速稳定性(尤其是在直线行驶时),使经验丰富的赛车手能够全力以赴。为了实现领先获胜的性能(这是决定您是冲在最前面还是被困在车队中间的关键因素),底盘几何形状和高转速四冲程发动机的宽功率带旨在最大限度地提高后轮牵引力。这一组合是久经考验的比赛获胜者,曾多次获得 AMA Supercross Lites 和 Motocross Lites 冠军。

2009 款车型信息 - Mototribu

KX250F 基础套件为经验丰富的赛车手提供了一个绝佳的平台,帮助他们在顶级比赛中获胜。高刚性铝制框架、悬挂组件和设置的设计专注于提供卓越的高速稳定性 - 尤其是在直线行驶时 - 使经验丰富的赛车手能够全力以赴。为了提供领先获胜的性能 - 这是一个关键因素,可能意味着在领先和获胜之间或被困在中间 - 底盘几何形状和高转速四冲程发动机的宽功率带旨在最大限度地提高后轮牵引力。该组合是经过验证的比赛获胜者,多次获得 AMA Supercross Lites 和 Motocross Lites 冠军。

2009 款车型信息 - Mototribu

KX250F 基础套件为经验丰富的赛车手提供了一个绝佳的平台,帮助他们在顶级比赛中获胜。高刚性铝制框架、悬挂组件和设置的设计专注于提供卓越的高速稳定性(尤其是在直线行驶时),使经验丰富的赛车手能够全力以赴。为了实现领先获胜的性能(这是决定您是冲在最前面还是被困在中间的关键因素),底盘几何形状和高转速四冲程发动机的宽功率带旨在最大限度地提高后轮牵引力。这一组合是久经考验的比赛获胜者,曾多次获得 AMA Supercross Lites 和 Motocross Lites 冠军。

2009 款车型信息 - Mototribu

KX250F 基础套件为经验丰富的赛车手提供了一个绝佳的平台,帮助他们在顶级比赛中获胜。高刚性铝制框架、悬挂组件和设置的设计专注于提供卓越的高速稳定性(尤其是在直线行驶时),使经验丰富的赛车手能够全力以赴。为了实现领先获胜的性能(这是决定您是冲在最前面还是被困在车队中间的关键因素),底盘几何形状和高转速四冲程发动机的宽功率带旨在最大限度地提高后轮牵引力。这一组合是久经考验的比赛获胜者,曾多次获得 AMA Supercross Lites 和 Motocross Lites 冠军。

2009 款车型信息 - Mototribu

KX250F 基础套件为经验丰富的赛车手提供了一个绝佳的平台,帮助他们在顶级比赛中获胜。高刚性铝制框架、悬挂组件和设置的设计专注于提供卓越的高速稳定性(尤其是在直线行驶时),使经验丰富的赛车手能够全力以赴。为了实现领先获胜的性能(这是决定您是冲在最前面还是被困在车队中间的关键因素),底盘几何形状和高转速四冲程发动机的宽功率带旨在最大限度地提高后轮牵引力。这一组合是久经考验的比赛获胜者,曾多次获得 AMA Supercross Lites 和 Motocross Lites 冠军。

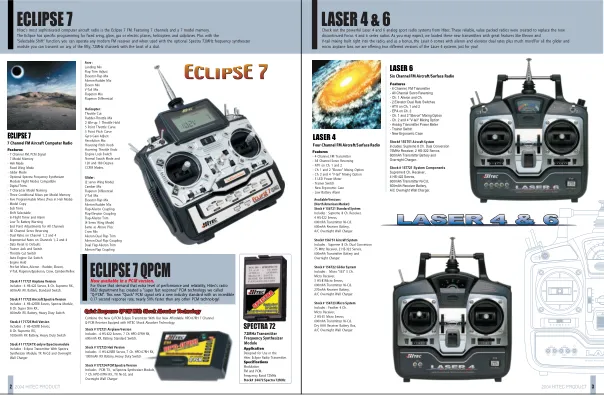

ECLIPSE7QPCM LASER 4 & 6 ECLIPSE 7 - 拉斯。梅克。我 。点

Hitec 发布了 Aggressor CRX 3 通道 FM 电脑手枪式无线电系统,大获成功。具有 20 种型号内存、高清图形 LCD 显示屏、数字微调、按钮式第三通道换档,以及易于编程的用户界面,其中包含任何人可能需要的所有花哨功能。CRX 肯定会受到赛车手和后院爱好者的欢迎。CRX 是一款真正的顶级竞赛级系统,同时仍考虑到运动用户;它是 Hitec 新款 Aggressor 手枪式无线电系列的绝佳补充。CRX 有几种不同的版本,所有版本都配有镍镉发射器和我们的标准隔夜壁式充电器。使用 Spectra 频率合成器模块和 Novak 合成接收器(限时)即可获得,再也不用购买其他水晶了!已经有几个 FM 接收器了?仅使用 Spectra 即可获得发射器,节省一些钱。