XiaoMi-AI文件搜索系统

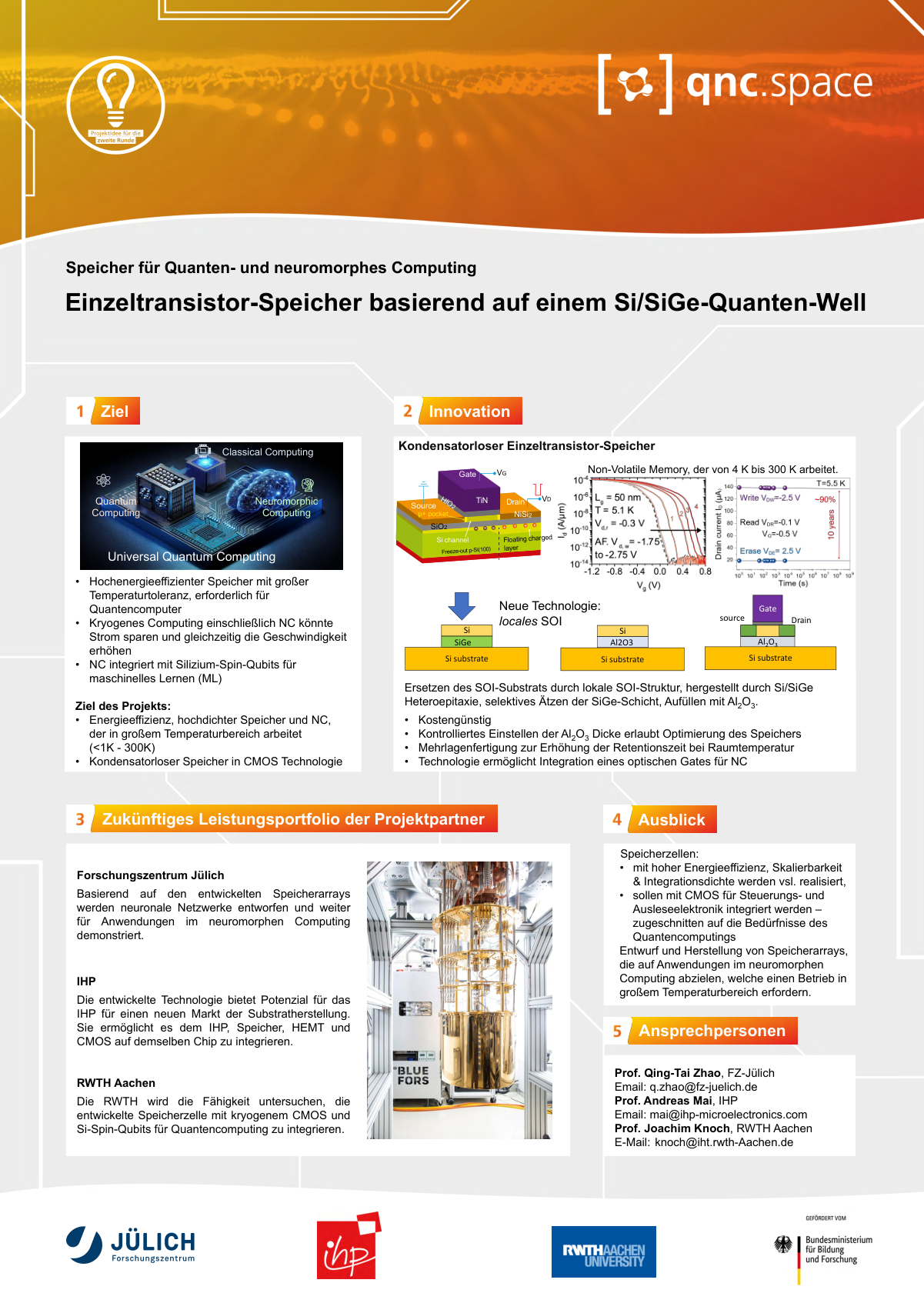

World File Search System基于 Si/SiGe 的单晶体管存储器...

存储单元:• 可能实现高能效、可扩展性和集成密度,• 将与 CMOS 集成用于控制和读出电子设备 - 根据量子计算的需求设计和制造存储阵列,旨在满足需要在宽温度范围内操作的神经形态计算应用。

四路串行持久性 SRAM 存储器

SRAM 闪存 EEPROM MRAM 非易失性 − √ √ √ 写入性能 √ − − √ 读取性能 √ − − √ 耐久性 √ − − √ 功率 − − − √ MRAM 是一种真正的随机存取存储器;允许在内存中随机进行读取和写入。MRAM 非常适合必须存储和检索数据而不会产生较大延迟损失的应用程序。它提供低延迟、低功耗、无限耐久性和可扩展的非易失性存储器技术。 ASxxxx208 具有串行外设接口 (SPI)。SPI 是一种同步接口,它使用单独的数据和时钟线路来帮助保持主机和从机的完美同步。时钟告诉接收器何时对数据线上的位进行采样。这可以是时钟信号的上升沿(从低到高)或下降沿(从高到低)或两个沿;有关更多详细信息,请参阅本数据表中的指令序列。当接收器检测到正确的边沿时,它可以锁存数据。 ASxxxx208 用双 CS# 连接两个四通道 SPI 设备,提供 8 位 I/O 数据路径。每个设备都可以使用自己的寄存器组进行配置和独立操作,由单独的 CS# 进行管理。ASxxxx208 采用 96 球 FBGA 封装。该封装具有单独的球,用于 CS1#、CLK1# 和 INT1(双四通道 SPI 设备 1)以及 CS2#、CLK2# 和 INT2(双四通道 SPI 设备 2)。该封装与类似的低功耗易失性和非易失性产品兼容。

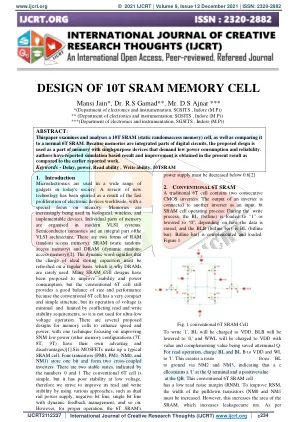

10T SRAM 存储器单元的设计

1. 简介 当今社会,微电子技术被广泛应用于各种设备中。电子设备在世界范围内的快速普及,促使人们开始审视新技术,尤其是存储器。存储器越来越多地用于生物、无线和可实现设备中。存储器的各个部分在现代 VLSI 系统中组织起来。半导体存储器是 VLSI 架构不可或缺的一部分。RAM(随机存取存储器)有两种形式:SRAM(静态随机存取存储器)和 DRAM(动态随机存取存储器)[2]。动态一词表示理想存储电容器的电荷必须定期刷新,这就是 DRAM 很少使用的原因。为了提高稳定性和功耗,已经提出了许多SRAM单元设计,但传统的6T单元仍然提供了尺寸和性能的良好平衡,因为传统的6T单元具有非常紧凑和简单的结构,但是其操作电压最小并且受到相互冲突的读写稳定性要求的限制,因此它不用于超低电压操作。有几种针对存储器单元的设计提案以提高速度和功率,其中一种技术专注于提高SNM的低功耗(其他存储器配置(7T,8T,9T)各有优缺点)[1]。六个MOSFET组成一个典型的SRAM单元。四个晶体管(PM0,PM1,NM0和NM1)存储一位并形成两个交叉耦合的反相器。有两种稳定状态,用数字 0 和 1 表示。传统的 6T 单元很简单,但在低压下稳定性较差,因此我们努力通过各种方法提高其读写稳定性,例如双轨电源、负位线、带动态反馈管理的单位线等。然而,为了正常运行,6T SRAM 的

高密度安全存储器 DDR3 SDRAM

4GB 512M x 64 W3J512M64X-XPB2X 800-1600 K=1.35,G=1.5 543 PBGA 23 毫米 x 32 毫米 C、I、M 4GB 512M x 72 W3J512M72X-XPB2X 800-1600 K=1.35,G=1.5 543 PBGA 23 毫米 x 32 毫米 C、I、M 4GB 512M x 64 W3J512M64X-XLB2X 800-1600 K=1.35,G=1.5 543 PBGA 23 毫米 x 32 毫米 C、I、M 4GB 512M x 72 W3J512M72X-XLB2X 800-1600 K=1.35,G=1.5 543 PBGA 23 毫米 x 32 毫米 C、I、M 4GB 高清 512M x 64 W3J512M64X(T)-XHDX 800-1600 K=1.35,G=1.5 399 PBGA 14 毫米 x 21.5 毫米 C、I、M 4GB 高清 512M x 72 W3J512M72X(T)-XHDX 800-1600 K=1.35,G=1.5 399 PBGA 14 毫米 x 21.5 毫米 C、I、M 8GB 8GB x 64 W3J1G64X-XPBX 800-1600 K=1.35,G=1.5 543 PBGA 24 毫米 x 32 毫米 C、I、M 8GB 8GB x 72 W3J1G72X-XPBX 800-1600 K=1.35,G=1.5 543 PBGA 24 毫米 x 32 毫米 C、I、M

第 4 章 系统单元

微型计算机有三种基本类型: 台式系统单元:包含系统的电子元件和选定的辅助存储器。鼠标、键盘、显示器等输入和输出设备位于系统单元外部。它可以水平或垂直放置。垂直单元称为“塔式模型”。 笔记本系统单元:便携且小得多。它们包含电子元件、选定的辅助存储器和输入设备(键盘和指点设备)。显示器位于系统单元外部,通过铰链与其相连。 个人数字助理 (PDA) 系统单元:最小,设计为一只手掌大小。它包含整个计算机系统,包括电子元件、辅助存储器和输入和输出设备

BJ8M608B - -深圳市博巨兴微电子科技有限公司

2.1 程序存储器 ROM(MTP) ......................................................................................................... 9 2.2 用户数据存储器( RAM ) ................................................................................................... 10 2.3 特殊寄存器( SFR ) ........................................................................................................... 11 2.4 CPU 内核常用 SFR ( PC/ACC/SP/IAP0/MP0/STATUS ) ................................................... 14 2.4.1 程序计数器 PC .............................................................................................................. 14 2.4.2 累加器 ACC .................................................................................................................. 14 2.4.3 堆栈指针 SP .................................................................................................................. 14 2.4.4 间接寻址寄存器 IAR0 、 MP0 ........................................................................................ 15 2.4.5 程序状态寄存器 STATUS ............................................................................................. 16

二维被动保护量子存储器的候选方案

量子纠错领域的一个有趣问题是找到一个物理系统,该系统承载着“被动保护的量子存储器”,即与自然想要纠正错误的环境耦合的编码量子位。迄今为止,仅在四个或更高的空间维度中才知道量子存储器能够抵抗有限温度效应。在这里,我们采用不同的方法,通过依赖驱动耗散环境来实现稳定的量子存储器。我们提出了一个新模型,即光子-伊辛模型,它似乎可以被动地纠正二维中的位翻转和相位翻转错误:由光子“猫量子位”组成的方格,这些量子位通过耗散项耦合,倾向于局部修复错误。受两个不同的 Z 2 对称性破坏相的启发,我们的方案依靠类伊辛耗散器来防止位翻转,并依靠驱动耗散光子环境来防止相位翻转。我们还讨论了实现光子-伊辛模型的可能方法。

电阻存储器分析和建模的参数提取技术

本文对用于提取电阻开关 (RS) 和建模参数的不同数值技术进行了修订。针对不同的电阻存储技术,计算了常用于估计可变性的置位和复位电压。还介绍了提取串联电阻的方法以及与电荷通量忆阻建模方法相关的参数。研究发现,获得的周期间 (C2C) 可变性取决于所使用的数值技术。这一结果很重要,它意味着在分析 C2C 可变性时,应描述提取技术以对不同的电阻存储技术进行公平比较。除了使用大量不同类型的电阻存储器的实验数据外,我们还采用了动力学蒙特卡罗 (kMC) 模拟来研究构成导电细丝 (CF) 的渗透路径的形成和断裂事件,这些细丝允许在丝状单极和双极器件中进行电阻开关操作。

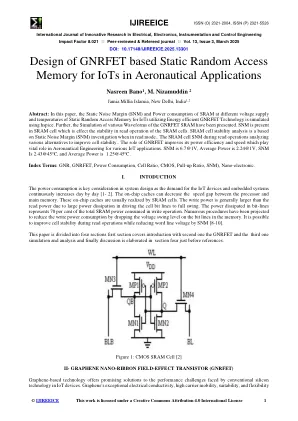

基于GNRFET的静态随机访问存储器的设计...

摘要:在本文中,使用HSPICE模拟了使用能源有效GNRFET技术的物联网的静态噪声边距(SNM)和SRAM在不同电压供应和静态随机访问记忆的温度下的功耗。此外,已经提出了GNRFET SRAM的各种波形的模拟。SNM存在于SRAM细胞中,这会影响SRAM细胞的读取操作的稳定性。SRAM细胞稳定性分析是一个基于静态噪声边缘(SNM)的研究。在阅读操作过程中,SRAM细胞SNM分析了各种替代方案以提高细胞稳定性。GNRFET的作用提高了其功率效率和速度,在各种物联网应用中在航空工程中起着至关重要的作用。snm是6.7@1v,平均功率为2.24@1v,snm为2.43@45 o C,平均功率为1.25@45 o C.索引条款:GNR,GNRFET,功耗,电池消耗,细胞比率,CMOS,CMOS,PURPIP RATIO,SNM,SNM),Nano-Electronic。

光量子存储器及其在量子通信系统中的应用

光量子存储器及其在量子通信系统中的应用 马利军、Oliver Slattery 和唐晓 美国国家标准与技术研究所,马里兰州盖瑟斯堡 20899,美国 lijun.ma@nist.gov oliver.slattery@nist.gov xiao.tang@nist.gov 光量子存储器是一种可以存储光子的量子态并以高保真度按需检索的装置。它正在成为一种必不可少的设备,以提高通信、计算、计量等领域使用的许多量子系统的安全性、速度、可扩展性和性能。在本文中,我们将特别考虑光量子存储器对量子通信系统的影响。在概述光量子存储器的理论和实验研究进展之后,我们将概述其在量子通信中的作用,包括作为光子源、光子干涉、量子密钥分发(QKD)、量子隐形传态、量子中继器和量子网络。 关键词:量子通信;量子密钥分发;量子存储器;量子网络;量子中继器。接受日期:2019年12月9日 发表日期:2020年1月16日 https://doi.org/10.6028/jres.125.002 1. 引言 量子通信是一种利用信息载体(如单光子)的量子特性,实现双方量子信息交换的技术。该技术有许多独特的应用,是经典通信系统中不可能实现的。目前,量子通信有两种主要应用:量子密钥分发(QKD)和量子纠缠分发。