XiaoMi-AI文件搜索系统

World File Search SystemS41598-024-72448-2.pdf

这项研究研究了垂直堆叠的CVD生长的RES 2 /MOS 2单极异质结构设备作为现场效应晶体管(FET)设备,其中Res 2上的RES 2充当排水管,而MOS 2在底部充当源。进行了RES 2 /MOS 2 FET设备的电气测量值,并针对不同VGS(闸门电压)(漏极电压)的ID(排水电流)(漏极电压)变化,显示了N型设备特性。此外,阈值电压是在栅极偏置电压上计算的,对应于〜12V。拟议的RES 2 /MOS 2 HeteroJunction FET设备的迁移率为60.97 cm 2 V -1 S -1。利用紫外线光学光谱和可见的紫外线光谱法提取了制造的VDW异质结构的带状结构,揭示了Res 2 /MOS 2界面处的2D电子气体(2DEG)的形成,从而探索了制造Fet的高载流子迁移率。通过跨异构结的屏障高度调节,研究了野外效应行为,并根据跨异构结的电荷传输提出了详细的解释。

重点介绍了商业SERS底物以及优化的Nanorough大区域SERS传感器:Raman研究

摘要使用带有电热模型的TCAD-Santaurus工具设计和优化了基于GAN纳米线的新垂直晶体管结构。具有准1D漂移区域的研究结构适用于在高度N掺杂的硅底物上与自下而上方法合成的GAN纳米线。对电性能的研究是各种Epi结构参数的函数,包括区域长度和掺杂水平,纳米线直径以及表面状态的影响。结果表明,优化的结构具有正常的阈值模式,其阈值电压高于0.8 V,并且表现出最小化的泄漏电流,州电阻较低,并且最大化的击穿电压。据我们所知,这是对基于GAN的纳米晶体管的首次详尽研究,为科学界提供了宝贵的见解,并有助于更深入地了解GAN NANOWIRE参数对设备性能的影响。据我们所知,这是对基于GAN的纳米晶体管的首次详尽研究,为科学界提供了宝贵的见解,并有助于更深入地了解GAN NANOWIRE参数对设备性能的影响。

使用声发射测试方法

曲线)。相关的声引起的电压信号显示为绿色点,即所谓的AE命中。在DB AE中绘制每个命中的峰值振幅(参考值1μV)。在给定的示例中,时间依赖性力曲线是非线性的,直至约为230 mn的接触力,而同时将许多AE命中率显示在23 dB ae的阈值电压上。这种效果是由于凹痕渗透到Al-Cu顶层的升高而渗透到质量变形的,凹痕深度正在增加的事实引起的(见图7a)。AE命中的数量及其峰值幅度与渗透深度增加成正比。在230 mn的接触力上方仅出现低振幅的孤立命中。在Al-Cu顶层的压痕上,SIO X层的破裂始于367 MN的接触力F C,峰值A峰为55.9 dB AE。在图中绘制了裂纹引起的AE命中的示例性波信号。6B,在整个信号持续时间内。[1]

SiC-MOSFET阈值电压漂移的测量与分析

法国里昂 摘要 碳化硅功率 MOSFET 在许多研究中用于提高电力电子转换器的效率或性能。然而,栅极氧化物技术弱点是碳化硅 MOSFET 晶体管的主要可靠性问题。阈值电压漂移是解决工业电源应用可靠性的关键现象。更好地理解栅极阈值电压漂移中隐含的现象非常重要。在此背景下,本文提出了一种基于 JEDEC 标准的静态老化测试,并研究和讨论了由此产生的栅极氧化物应力。进行了补充测试,包括动态可靠性和栅极氧化物特性,例如电荷泵技术。获得的结果用于为当前有关 SiC MOSFET 稳健性的讨论增添见解。此外,还详细介绍了测试台和测量协议。 * 通讯作者 quentin.molin@supergrid-institute.com 电话:+33 6 68 30 16 52 1. 简介 由于 SiC 具有比硅更优越的电气性能,因此它是一种很有前途的高压高温器件材料。然而,仍有许多可靠性问题有待解决,例如氧化物退化 [1]、阈值电压不稳定性 [2]、[3] 和短路行为 [4]、[5] 和 [6]。其中一些关键点对于开发用于工业应用的可靠功率器件至关重要 [7]。

耐变异感测放大器电路的设计

摘要 在 DRAM 和 SRAM 等深亚微米存储器中,准确感测位线电压变得非常具有挑战性,因为制造工艺的固有变化导致晶体管特性失配,这带来了严重的挑战,导致电路故障和产量下降。本文解决了这些问题,并将补偿方案应用于各种感测放大器的原理图,从而对工艺引起的变化具有很高的容忍度。使用 DGFinFET 设计的原理图利用增强的自补偿技术来克服物理晶体管特性的差异。使用蒙特卡罗技术重建晶体管失配(阈值电压,V t ),表明即使在 40-50mV 的严重 V t 失配下,所提出的 CCLSA 原理图也能正确运行。将这些结果与文献中报道的相应电路进行了速度、面积和产量的比较。与未补偿的设计相比,该设计还提供了高达 20-30% 的产量,并且降低了电路和性能的复杂性。这些电路在 45nm 和 32nm 技术节点上很容易实现。关键词:补偿、工艺变化、DRAM、FinFET 感测放大器、稳健性

光伏辅助自Vth取消CMOS整流器...

摘要 开发了一种用于射频能量收集的高效 CMOS 整流器(采用 0.18 µ m CMOS 技术)。为了在极低输入功率条件下也能高效运行,采用自 Vth 抵消 (SVC) 和光伏 (PV) 辅助技术的有效组合实现了基于倍压器的整流器。在该整流器中,二极管连接 MOSFET 的阈值电压 (Vth) 由直流偏置电压补偿,该偏置电压不仅由片上 PV 电池产生,还由整流器本身的输出电压产生。因此,即使在低输入功率条件下,整流器也能高效运行。此外,采用了使用简单 pn 二极管的偏置电压限制器来有效调节过度的 Vth 补偿,并在宽功率范围内实现整流器的高运行效率。在输入功率为 − 15 dBm、频率为 1 GHz、输出负载电阻为 10 k Ω 和光照度为 10 mW/m 2 的情况下,射频到直流功率转换效率 (PCE) 达到 30.8%。关键词:能量收集、无线电波、光伏、功率转换效率、整流器分类:能量收集设备、电路和模块

利用电子风力对伽马射线辐照的 GaN HEMT 进行非热退火

电子产品中的辐射损伤减轻仍然是一个挑战,因为唯一成熟的技术——热退火,并不能保证获得良好的结果。在本研究中,我们介绍了一种非热退火技术,其中使用来自非常短持续时间和高电流密度脉冲的电子动量来瞄准和调动缺陷。该技术在 60 Co 伽马辐照(5 × 10 6 拉德剂量和 180 × 10 3 拉德 h − 1 剂量率)GaN 高电子迁移率晶体管上进行了演示。在 30 °C 或更低温度下,饱和电流和最大跨导完全恢复,阈值电压部分恢复。相比之下,300 °C 下的热退火大多使辐照后特性恶化。拉曼光谱显示缺陷增加,从而降低了二维电子气 (2DEG) 浓度并增加了载流子散射。由于电子动量力不适用于聚合物表面钝化,因此所提出的技术无法恢复栅极漏电流,但性能优于热退火。这项研究的结果可能有助于减轻电子器件中某些形式的辐射损伤,而这些损伤很难通过热退火实现。© 2022 电化学学会(“ ECS ” )。由 IOP Publishing Limited 代表 ECS 出版。[DOI:10.1149/2162-8777/ ac7f5a ]

采用极化诱导掺杂的 Ga2O3 场效应晶体管

摘要 III 族氮化物和β 相氧化镓(β -Ga 2 O 3 )是目前研究较为深入的两种用于电力电子的宽带隙半导体材料。由于两种材料体系之间的晶格失配度相对较小,且可以利用体相 AlN、GaN 和β -Ga 2 O 3 衬底,因此已经实现了在β -Ga 2 O 3 上外延生长 III 族氮化物或反之亦然。然而,将两种材料体系集成在一起来设计功率器件仍然缺乏。本文数值研究了 AlN/β -Ga 2 O 3 异质结构,利用极化诱导掺杂来实现高性能增强型晶体管。受 AlN/β -Ga 2 O 3 界面极化效应的影响,沟道中的二维电子气浓度最高可达 8.1 × 10 19 cm −3。在沟道顶部引入p-GaN栅极,最终实现了具有可调正阈值电压的常关型AlN/β-Ga 2 O 3场效应晶体管。此外,我们插入了非故意掺杂的GaN背阻挡层以抑制漏极漏电流。最后,为了实现高性能III族氮化物/Ga 2 O 3基功率器件,我们进一步研究和分析了具有不同结构参数的器件的传输和输出特性。

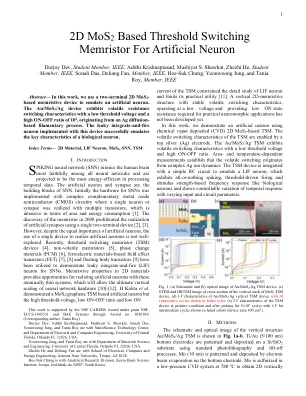

基于 2D MoS2 的阈值开关忆阻器用于...

在所有神经网络中,PIKING 神经网络 (SNN) 最忠实地模拟了人脑,并且被认为是处理时间数据最节能的网络。人工神经元和突触是 SNN 的组成部分。最初,SNN 的硬件采用复杂的互补金属氧化物半导体 (CMOS) 电路实现,其中单个神经元或突触由多个晶体管实现,这在面积和能耗方面非常密集 [1]。2008 年忆阻器的发现促进了使用单个双端器件实现人工突触的发展 [2],[3]。然而,尽管人工神经元同样重要,但使用单个器件实现人工神经元的研究还不够深入。最近,阈值开关忆阻器 (TSM) 器件 [4]、非挥发性忆阻器 [5]、相变材料 (PCM) [6]、基于铁电材料的场效应晶体管 (FET) [7]、[8] 和浮体晶体管 [9] 已被用于演示用于 SNN 的漏电积分激发 (LIF) 神经元。二维材料的忆阻特性为利用这些原子级薄系统实现人工神经元提供了机会,这将实现神经网络硬件的最终垂直扩展 [10]-[12]。H Kalita 等人演示了一种基于 MoS 2 /石墨烯 TSM 的人工神经元,但阈值电压高、开关比低、导通时间短。

通道宽度对顶门自我对准的Coplanar Igzo薄膜晶体管的电气性能降解的定量分析

Dong-Ho Lee 1 , Hwan-Seok Jeong 1 , Yeong-Gil Kim 1 , Myeong-Ho Kim 2 , Kyoung Seok Son 2 , Jun Hyung Lim 2 , Sang-Hun Song 1,* , and Hyuck-In Kwon 1,* Abstract —In this study, a quantitative analysis was conducted on the effects of channel width on electrical performance degradation induced by self-heating stress (SHS) in顶门自我对准的共蓝淀粉锌氧化物(IGZO)薄膜晶体管(TFTS)。从SHS之前和之后获得的转移和电容 - 电压曲线,我们透露,TFT的电性能沿通道长度方向不均匀地降解,并且该降解的程度在具有较宽通道宽度的TFT中更为显着。在制成的Igzo TFT中,SHS下的阈值电压偏移(δVTh)主要归因于Igzo活性区域的浅供体状态的密度和受体样的深状态的增加,并且电子陷入了Sio X Gate Patectric中的快速和慢速陷阱。此外,我们使用基于状态δVTh Th Th的TFTs的TFTS的子仪密度来进行SHS诱导的δv Th起源于每个降解机制。尽管每种降解机制的每一个δv th都随着通道宽度的增加而增加,但增加了电子捕获到Sio X Gate中的慢陷阱