XiaoMi-AI文件搜索系统

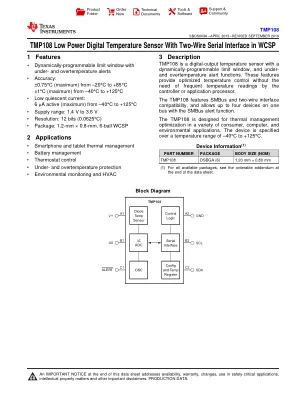

World File Search SystemTMP108 低功耗数字温度传感器,带 WCSP 封装的双线串行接口

从 TMP108 读取时,写入操作存储在指针寄存器中的最后一个值用于确定读取操作读取哪个寄存器。要更改读取操作的寄存器指针,必须将新值写入指针寄存器。此操作通过发出 R/W 位低的从地址字节,然后发出指针寄存器字节来完成。无需其他数据。然后,主机可以生成起始条件并发送 R/W 位高的从地址字节以启动读取命令。有关此序列的详细信息,请参见图 3。如果需要从同一寄存器重复读取,则无需连续发送指针寄存器字节,因为 TMP108 会存储指针寄存器值,直到下一次写入操作更改它为止。

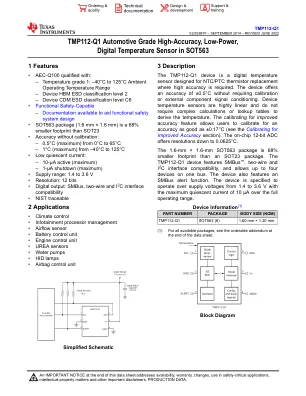

TMP112-Q1 汽车级高精度、低功耗数字温度传感器数据表 (Rev. F)

每次温度测量转换的数字输出都存储在只读温度寄存器中。TMP112-Q1 器件的温度寄存器配置为 12 位只读寄存器(在配置寄存器中将 EM 位设置为 0;请参阅扩展模式 (EM) 部分),或配置为 13 位只读寄存器(在配置寄存器中将 EM 位设置为 1),用于存储最新转换的输出。必须读取两个字节才能获得数据,如表 8-8 所示。字节 1 是最高有效字节 (MSB),后跟字节 2,即最低有效字节 (LSB)。前 12 位(扩展模式下为 13 位)用于指示温度。如果不需要该信息,则不必读取最低有效字节。温度的数据格式如表 8-2 和表 8-3 所示。一个 LSB 等于 0.0625°C。负数以二进制补码格式表示。上电或复位后,温度寄存器读数为 0°C,直到第一次转换完成。字节 2 的位 D0 表示正常模式(EM 位等于 0)或扩展模式(EM 位等于 1),可用于区分两种温度寄存器数据格式。温度寄存器中未使用的位始终读取 0。

WCSP 封装带双线接口的低功耗数字温度传感器数据表 (Rev. A)

从 TMP108 读取时,写入操作存储在指针寄存器中的最后一个值用于确定读取操作读取哪个寄存器。要更改读取操作的寄存器指针,必须将新值写入指针寄存器。此操作通过发出 R/W 位为低的从属地址字节,然后发出指针寄存器字节来完成。无需其他数据。然后,主机可以生成启动条件并发送 R/W 位为高的从属地址字节以启动读取命令。有关此序列的详细信息,请参见图 3。如果需要从同一寄存器重复读取,则无需连续发送指针寄存器字节,因为 TMP108 会存储指针寄存器值,直到下一次写入操作更改它为止。

4242-VPK 小尺寸低功耗三通道和四通道数字隔离器 (Rev. F)

(1) 超出绝对最大额定值所列的应力可能会对器件造成永久性损坏。这些只是应力额定值,并不表示器件在这些或任何超出建议工作条件所列条件的条件下能够正常工作。长时间暴露在绝对最大额定条件下可能会影响器件的可靠性。

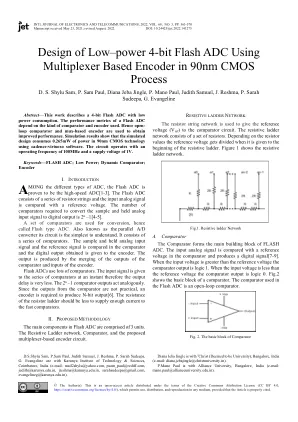

采用 90nm CMOS 工艺多路复用器编码器设计低功耗 4 位闪存 ADC

在各种 ADC 架构中,FLASH ADC 被证明是高性能 ADC。所提出的 ADC 由基于多路复用器的编码器、开环比较器和电阻梯形网络组成。所提出的 ADC 采用 90nm CMOS 技术进行模拟。所提出的 ADC 的主要优点是静态功耗低。这是通过将基于多路复用器的编码器集成到 Flash ADC 中实现的。所提出的 ADC 的功耗为 26.65µw,输入电压为 1V,频率为 100MHz。设计的 Flash ADC 可用于高速应用。

采用混合相移方案的 56 至 66 GHz CMOS 低功耗相控阵接收机前端

摘要 — 本文介绍了一种体积小、功耗低的毫米波相控阵接收机前端。本振 (LO) 和射频 (RF) 相移方案相结合,用于降低功耗和 RF 路径损耗。此外,在有源电路的实现中,采用了体隔离技术,以最少的级数实现更高的功率增益。该技术还用于 RF 路径移相器开关以减轻损耗。为了验证所提出的架构,采用 65 nm 体 CMOS 工艺制造了一个单元件 56 至 66 GHz 相控阵接收机前端。根据测量结果,接收机实现了 ∼ 14.85 dB 的功率增益和 5.7 dB 的最小噪声系数 (NF)。测得的平均 RMS 相位和增益误差分别为 ∼ 3.5 ◦ 和 ∼ 0.45 dB。接收器链的输入 1dB 压缩点 (P − 1dB ) 约为 − 19 dBm。完整的接收器(包括有源平衡-不平衡转换器和所需缓冲器(不包括 LO))在 1 V 电源下消耗约 50 mW 功率,不包括焊盘,占用硅片面积为 0.93 mm 2 。

TMP108 低功耗数字温度传感器,具有 WCSP 封装中的两线串行接口

从 TMP108 读取时,写入操作存储在指针寄存器中的最后一个值用于确定读取操作读取哪个寄存器。要更改读取操作的寄存器指针,必须将新值写入指针寄存器。此操作通过发出 R/W 位为低的从属地址字节,然后发出指针寄存器字节来完成。无需其他数据。然后,主机可以生成启动条件并发送 R/W 位为高的从属地址字节以启动读取命令。有关此序列的详细信息,请参见图 3。如果需要从同一寄存器重复读取,则无需连续发送指针寄存器字节,因为 TMP108 会存储指针寄存器值,直到下一次写入操作更改它为止。

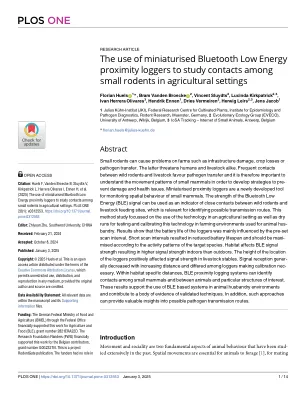

使用微型蓝牙低功耗近距离记录器研究农业环境中小型啮齿动物之间的接触

小型啮齿动物会给农场带来问题,例如基础设施损坏、农作物损失或病原体传播。后者对人类和牲畜都构成威胁。野生啮齿动物和牲畜之间的频繁接触有利于病原体传播,因此了解小型哺乳动物的运动模式对于制定预防损害和健康问题的策略非常重要。微型近距离记录器是一种新开发的用于监测小型哺乳动物空间行为的工具。蓝牙低功耗 (BLE) 信号的强度可用作野生啮齿动物与牲畜饲养地点密切接触的指标,这对于识别可能的传播途径很重要。该方法研究侧重于该技术在农业环境中的使用以及在用于畜牧业的农业环境中测试和校准该技术的试运行。结果表明,记录器的电池寿命主要受预设扫描间隔的影响。短扫描间隔会导致电池寿命缩短,应根据目标物种的活动模式最大化。栖息地会影响 BLE 信号强度,导致室内信号强度高于室外。记录器位置的高度对牲畜圈内的信号强度有积极影响。信号接收通常随着距离的增加而减小,并且不同记录器的信号接收也不同,因此需要进行校准。在特定栖息地的距离内,BLE 近距离记录系统可以识别小型哺乳动物之间以及动物与特定结构之间的接触。这些结果支持在畜牧业环境中使用基于 BLE 的系统,并为经过验证的技术提供了大量证据。此外,这种方法可以为可能的病原体传播途径提供有价值的见解。

TMP117 高精度、低功耗、数字温度传感器,带 SMBus™ 和 I2C 兼容接口数据表 (Rev. D)

6.1 绝对最大额定值 ...................................................... 5 6.2 ESD 额定值 .............................................................. 5 6.3 建议工作条件 .............................................................. 5 6.4 热信息 ...................................................................... 5 6.5 电气特性 ...................................................................... 6 6.6 开关特性 ...................................................................... 7 6.7 双线接口时序 ............................................................. 7 6.8 时序图 ...................................................................... 8 6.9 典型特性 ...................................................................... 8

适用于低功耗便携式应用的全集成 180 nm CMOS 1.2 V 低压差稳压器

长寿命自主便携式和可穿戴设备越来越多地出现 [1-8],对系统小型化和降低功耗的要求使高效电源管理单元 (PMU) 的设计成为首要问题,其中低压差 (LDO) 稳压器发挥着关键作用 [9-13]。如图 1 所示,在电池供电系统中,在电池电压和偏置特定系统模块所需的负载电流发生大幅变化的情况下,LDO 会从电池电压 V BAT 产生稳定、低噪声和精确的电源电压 V out ,通常会使用多个 LDO 来优化每个模块的功耗,从而优化整体电源效率。传统 LDO 依靠位于输出节点的外部 µ F 电容来保证稳定性,同时尽量减少瞬态工作下 V out 的变化 [14-16]。尽管如此,系统功率和尺寸的降低正导致完整的片上系统 (SoC) 设备的发展,其中所有组件都需要完全集成。实施低成本片上系统解决方案的一个关键条件是与互补金属氧化物半导体 (CMOS) 技术的兼容性。这反过来又与低压合规性有关,因为随着 CMOS 技术的缩小,电源电压也会缩小,非常接近 MOS 晶体管的阈值电压,因此在设计这种低压电路时必须遵循新策略。因此,无 CMOS 电容器低压差稳压器的设计已成为一个有前途的研究课题,需要低压架构和替代的片上补偿技术,以保持系统在整个工作范围内的稳定性,同时保持调节性能。此外,便携式设备的一个关键参数是功耗,因为它决定了电池寿命。这意味着使用低静态电流 I q 。然而,降低 Iq 会降低动态性能:最大输出电流受到限制,从而限制了诸如转换速率和稳定时间等参数。这就需要引入瞬态增强电路技术来平衡动态性能,同时将对功率效率和电路复杂性的影响降至最低。