XiaoMi-AI文件搜索系统

World File Search System第 2 单元 计算机系统

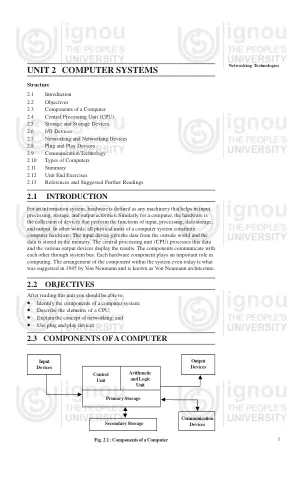

对于信息系统,硬件被定义为任何有助于输入、处理、存储和输出活动的机器。同样,对于计算机来说,硬件是执行输入、处理、数据存储和输出功能的设备的集合。换句话说,计算机系统的所有物理单元都构成了计算机硬件。输入设备从外界获取数据,数据存储在内存中。中央处理单元 (CPU) 处理这些数据,各种输出设备显示结果。组件通过系统总线相互通信。每个硬件组件在计算中都发挥着重要作用。即使在今天,系统内组件的排列方式也是冯·诺依曼在 1945 年提出的,被称为冯·诺依曼架构。

博士約翰·冯·諾伊曼

约翰·冯·诺依曼博士在美国弹道导弹计划的发展中发挥了关键作用。1953 年,他成为空军战略导弹评估委员会主席。该委员会就该部门管辖的所有导弹项目向空军部长提供建议和推荐。1954 年,他担任 ATLAS(后来的 ICBM)科学咨询委员会主席,负责监督 ATLAS 的进展并寻求加快导弹的开发。作为两个委员会的主席,冯·诺依曼博士提出了使用弹道导弹运载核武器的可行性。他认为苏联在洲际弹道导弹的发展方面具有优势,并预测到 20 世纪 50 年代末美国和苏联之间的导弹差距将非常明显。在没有更多资金的情况下,可投入使用的ATLAS洲际弹道导弹的研发最早也要到1963年才能完成。在冯·诺依曼委员会的建议和特雷弗·加德纳(时任美国空军研究与发展助理部长)的劝说下,美国加快了导弹计划的推进速度,并于1958年12月成功发射了一枚ATLAS导弹。

见证负条件熵

具有负条件冯诺依曼熵的量子态在多种信息论协议中提供了量子优势,包括超密集编码、状态合并、分布式私有随机性提炼和单向纠缠提炼。虽然纠缠是一种重要资源,但只有一部分纠缠态具有负条件冯诺依曼熵。在这项工作中,我们将具有非负条件冯诺依曼熵的密度矩阵类描述为凸和紧的。这使我们能够证明存在一个 Hermitian 算子(见证人),用于检测任意维度二分系统中具有负条件熵的状态。我们展示了两种此类见证人的构造。对于其中一种构造,状态中见证人的期望值是状态条件熵的上限。我们提出了一个问题,即获得状态条件熵集的严格上限,其中算子给出相同的期望值。我们对两个量子比特的情况用数字方法解决了这个凸优化问题,发现这提高了我们证人的实用性。我们还发现,对于特定证人,估计的严格上限与 Werner 状态的条件熵值相匹配。我们阐明了我们的工作在检测几个协议中的有用状态方面的实用性。

Changying Ding

3. C. Ding,S. Kunnawalkam Elayavalli,论相对双精确群冯诺依曼代数的结构,arXiv:2211.05298,数学物理通讯,第 405 卷,第 104 期,2024 年。

采用混合 CMOS-RRAM 集成的混合信号神经形态计算电路

随着深度神经网络 (DNN) 在嵌入式设备上的广泛应用,硬件的能效和尺寸成为关注焦点。例如,最近基于 Arduino 的 MAIXDuino 套件集成了用于卷积神经网络 (CNN) 的 K210 神经网络处理器,旨在开发嵌入式人工智能 (AI) 和物联网 (IoT) 解决方案 [1],[2]。在这种 Edge-AI 加速器专用集成电路 (ASIC) 中,DNN 模型在图形处理单元 (GPU) 上使用基于梯度下降的反向传播或 Backprop 算法 [3]–[5] 进行离线训练,然后“传输”到“推理”ASIC。反向传播是计算密集型的,由于冯诺依曼瓶颈,大量数据在内存和 CNN 加速器之间不断穿梭,因此会消耗大量能量。人们越来越重视创新“非冯·诺依曼”架构,即在内存内部执行计算。此类架构有望利用超越摩尔或后 CMOS 非易失性存储器 (NVM) 技术 [6]。这需要对整个设备、电路和算法层次结构中的非冯·诺依曼计算架构进行跨层研究。神经启发或神经形态片上系统 (NeuSoC) 架构将内存计算与基于稀疏尖峰的计算和通信相结合,以实现接近生物大脑能效的超低功耗运行 [7]。基于 NVM 的计算架构采用 1R 或 1T1R 交叉开关或交叉点架构,其中 DNN 权重存储在 NVM 单元的状态中,神经元驻留在

动力系统和 C∗-代数的交叉积

拓扑 C ∗ -代数 测度理论 冯·诺依曼代数 概率论 自由概率论与量子概率 微分几何 非交换几何 (紧)群 紧量子群 信息论 量子信息论 复分析 自由分析

arXiv:2306.14566v2 [quant-ph] 2024 年 2 月 11 日

我们提出了一种称为量子互信息神经估计 (QMINE) 的量子机器学习方法,用于估计冯·诺依曼熵和量子互信息,这是量子信息理论的基本属性。这里提出的 QMINE 基本上利用了量子神经网络 (QNN) 技术,以最小化确定冯·诺依曼熵的损失函数,从而确定量子互信息,由于量子叠加和纠缠,人们认为它比传统神经网络更能处理量子数据集。为了创建精确的损失函数,我们提出了一种量子 Donsker-Varadhan 表示 (QDVR),它是经典 Donsker-Varadhan 表示的量子类似物。通过利用参数化量子电路上的参数移位规则,我们可以有效地实现和优化 QNN,并使用 QMINE 技术估计量子熵。此外,数值观测支持我们对 QDVR 的预测,并证明了 QMINE 的良好性能。

使真正的忆阻内存处理更快且......

摘要 — 忆阻技术是替代传统内存技术的有吸引力的候选技术,并且还可以使用一种称为“状态逻辑”的技术来执行逻辑和算术运算。将数据存储和计算结合在内存阵列中可以实现一种新颖的非冯·诺依曼架构,其中两种操作都在忆阻内存处理单元 (mMPU) 中执行。mMPU 依赖于在不改变基本内存阵列结构的情况下向忆阻内存单元添加计算能力。使用 mMPU 可以缓解冯·诺依曼机器对性能和能耗的主要限制,即 CPU 和内存之间的数据传输。这里讨论了 mMPU 的各个方面,包括其架构和对计算系统和软件的影响,以及检查微架构方面。我们展示了如何改进 mMPU 以加速不同的应用程序,以及如何在 mMPU 操作中改进忆阻器的可靠性差的问题。

![arXiv:2306.14566v2 [quant-ph] 2024 年 2 月 11 日](/simg/5\5ab1cdb684d543a1dae744e6eda012859bace99e.webp)