XiaoMi-AI文件搜索系统

World File Search System利用低功耗人工智能超声波扩大乳腺癌筛查范围

https://www.researchgate.net/publication/343361013_DrJ_An_Artificial_Intelligence_Powered_Ultrasonography_Breast_Cancer_Preliminary_Screening_Solution 。 3 结果由 iCare365 Technologies 提供;并非基于英特尔测量的数据。性能因使用、配置和其他因素而异。了解更多信息,请访问 https://www.intel.com/PerformanceIndex 。英特尔不控制或审核第三方数据。您应该咨询其他来源以评估准确性。英特尔技术可能需要启用硬件、软件或服务激活。您的成本和结果可能会有所不同。© 英特尔公司。英特尔、英特尔徽标和其他英特尔标志是英特尔公司或其子公司的商标。其他名称和品牌可能是其他财产。0922/EH/MESH/349367-001US

受大脑神经调节信号启发的低功耗机器学习架构

摘要:我们提出了一种受生物大脑中调节神经递质机制启发的迁移学习方法,并探索神经形态硬件的应用。在该方法中,人工神经网络的预训练权重保持不变,并通过补充偏差输入操纵每个神经元的触发灵敏度来学习新的类似任务。我们将其称为神经调节调谐 (NT)。我们通过经验证明,神经调节调谐在前馈深度学习和脉冲神经网络架构中的图像识别领域产生的结果与传统微调 (TFT) 方法相当。在我们的测试中,与传统微调方法相比,NT 将要训练的参数数量减少了四个数量级。我们进一步证明,神经调节调谐可以在模拟硬件中实现为具有可变电源电压的电流源。我们的模拟神经元设计实现了泄漏积分和触发模型,其中三个双向二进制缩放电流源组成了突触。通过与每个突触相关的可调功率域应用近似于调节神经递质机制的信号。我们使用高精度仿真工具验证了电路设计的可行性,并提出了一种使用集成模拟电路高效实现神经调节的方法,该电路的功耗比数字硬件(GPU/CPU)低得多。

基于超薄 HfO2/Al2O3 双层的可靠 1T1R RRAM 电子突触,具有低功耗,可用于神经形态计算

1 西安交通大学电子材料研究实验室,教育部重点实验室,国际电介质研究中心,电子科学与工程学院,微纳制造与测试技术国际联合实验室,西安 710049,中国 2 中国科学院微电子研究所,微电子器件与集成技术重点实验室,北京 100029,中国 3 中国科学院大学,北京 100049,中国 4 西安交通大学机械制造系统工程国家重点实验室 & 微纳制造与测试技术国际联合实验室,西安 710049,中国 5 IHP-Leibniz-Institut für innovative Mikroelektronik,Im Technologiepark 25, 15236 Frankfurt,德国 6 上海交通大学信息功能材料国家重点实验室中国科学院微系统与信息技术研究所,上海市长宁路 865 号,邮编 200050,中华人民共和国 7 这些作者对这项工作做出了同等贡献。∗ 任何通讯作者均应致函。

低功耗 AI 加速器的最新发展

摘要:随着机器学习和人工智能的持续快速发展,以及摩尔定律的日益临近,架构设计的新途径和新想法正在被创造和利用。其中一种途径是尽可能靠近用户(即在边缘)加速人工智能,以减少延迟并提高性能。因此,研究人员开发了低功耗人工智能加速器,专门用于加速边缘设备上的机器学习和人工智能。在本文中,我们概述了 2019 年至 2022 年之间的低功耗人工智能加速器。本文根据加速目标和功耗对低功耗人工智能加速器进行了定义。在本次调查中,我们介绍并讨论了 79 种低功耗人工智能加速器。所审查的加速器基于五个标准进行讨论:(i)功率、性能和功率效率,(ii)加速目标,(iii)算术精度,(iv)神经形态加速器,以及(v)行业与学术加速器。 CNN 和 DNN 是最受欢迎的加速器目标,而 Transformers 和 SNN 正在崛起。

HammerScope:使用 Rowhammer 观察 DRAM 功耗

内存单元尺寸的不断减小提高了内存密度并降低了功耗,但也影响了其可靠性。Rowhammer 攻击利用这种降低的可靠性来诱导内存中的位翻转,而无需直接访问这些位。大多数 Rowhammer 攻击都以软件完整性为目标,但最近的一些攻击表明它可用于破坏机密性。延续这一趋势,我们在本文中观察到 Rowhammer 攻击与内存瞬时功耗密切相关。我们利用这一观察结果设计了 HammerScope,这是一种基于 Rowhammer 的攻击技术,用于测量内存单元的功耗。由于功耗与内存的活动水平相关,因此 HammerScope 允许攻击者推断内存活动。为了展示 HammerScope 的攻击能力,我们使用它发起了三次信息泄露攻击。我们首先展示了 HammerScope 可用于破坏内核地址空间布局随机化 (KASLR)。我们的第二次攻击使用内存活动作为 Spectre 攻击的隐蔽通道,使我们能够泄露操作系统内核的信息。最后,我们演示了如何使用 HammerScope 进行网站指纹识别,从而泄露用户隐私。我们的工作证明了找到 Rowhammer 攻击的系统解决方案的重要性。

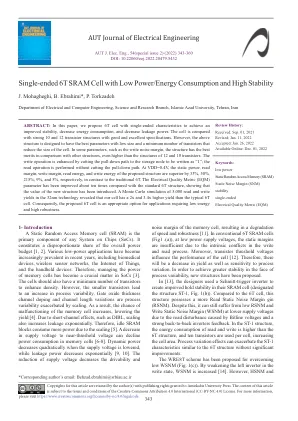

低功耗、高稳定性的单端 6T SRAM 单元

摘要:本文提出了一种具有单端特性的 6T 单元,以提高稳定性、降低能耗、降低漏电功率。该单元与规格优良的 10 和 12 晶体管结构进行了比较。然而,上述结构设计为具有最佳参数,尺寸小,晶体管数量最少,从而减小了单元尺寸。在某些参数方面,例如写入噪声容限,该结构与其他结构相比具有最佳优点,甚至高于 12 和 10 晶体管的结构。通过切断要写入为“1”的存储节点的下拉路径来增强写入操作;读取操作无需切断下拉路径即可执行。在 VDD=0.4V 时,与传统的 6T 相比,所提出的结构的静态功率、读取容限、写入容限、读取能量和写入能量分别优越 33%、50%、215%、9% 和 5%。与标准 6T 结构相比,电气质量指标 (EQM) 参数提高了约十倍,表明新结构的价值已经得到体现。对 32nm 技术中 5,000 次读写产量的蒙特卡洛模拟表明,我们的单元产量比典型的 6T 单元高出 2 倍和 3.4 倍。因此,对于需要低能耗和高稳健性的应用,建议的 6T 单元是一个合适的选择。

用于深度神经网络分层图像识别的超低功耗图像信号处理器

稿件于 2020 年 8 月 30 日收到;2020 年 11 月 4 日修订;2020 年 11 月 22 日接受。出版日期 2020 年 12 月 14 日;当前版本日期 2021 年 3 月 26 日。本文经副主编 Yusuke Oike 批准。这项工作得到了索尼半导体解决方案公司/索尼电子公司的支持。(通讯作者:Hyochan An。)Hyochan An、Qirui Zhang、Kyojin D. Choo、Shiyu Liu、Bowen Liu、Hengfei Zhong、David Blaauw、Ronald Dreslinski、Hun Seok Kim 和 Dennis Sylvester 就职于密歇根大学电气与计算机工程系,密歇根州安娜堡 48109 美国(电子邮件:hyochan@umich.edu)。Sam Schiferl 就职于亚马逊,华盛顿州西雅图 98109 美国。 Siddharth Venkatesan 就职于亚马逊公司,美国加利福尼亚州圣克拉拉 95054。Tim Wesley 就职于 MemryX 公司,美国密歇根州安娜堡 48105。Jingcheng Wang 和 H. Zhong 就职于苹果公司,美国加利福尼亚州库比蒂诺 95014。Ziyun Li 就职于 Facebook 公司,美国华盛顿州雷德蒙德 98052。Luyao Gong 就职于谷歌公司,美国加利福尼亚州山景城 94043。本文中一个或多个图片的彩色版本可在 https://doi.org/10.1109/JSSC.2020.3041858 上找到。数字对象标识符 10.1109/JSSC.2020.3041858

使用有源电感和 1 /f 噪声消除的宽带低功耗 RF 至 BB 电流复用接收器,适用于 L 波段应用

摘要 本文提出了一种低功耗宽带射频到基带 (BB) 电流复用接收器 (CRR) 前端,它同时利用了 1/f 噪声消除 (NC) 技术和有源电感器 (AI),工作频率为 1 GHz 至 1.7 GHz,适用于 L 波段应用,包括那些需要高调制带宽的应用。CRR 前端采用单电源,并与 BB 电路共享低噪声跨导放大器 (LNTA) 的偏置电流,以降低功耗。为了最大限度地减少下变频之前射频 (RF) 信号的损失,高阻抗 AI 电路将混频器输入与 CRR 输出节点隔离。1/f NC 电路可抑制泄漏到输出的 LNTA 低频噪声。带有 gm 增强的共栅极 LNTA 以及单端到差分 LC 平衡-不平衡转换器用于增强输入匹配、变频增益和噪声系数 (NF)。所提出的接收器采用 TSMC 130 nm CMOS 工艺制造,占用有效面积为 0.54mm 2 。输入匹配 (S 11 ) 在 1 GHz 至 1 . 7 GHz 范围内低于 − 10 dB。在本振 (LO) 频率为 1 . 3 GHz、中频 (IF) 为 10 MHz 和默认电流设置下,CRR 实现了 41 . 5 dB 的转换增益、6 . 5 dB 的双边带 (DSB) NF 和 − 28.2 dBm 的 IIP3,同时消耗 1.66 mA 电流,电源电压为 1 . 2 V。

使用 Rowhammer 观察 DRAM 功耗

内存单元尺寸的不断减小提高了内存密度并降低了功耗,但也影响了其可靠性。Rowhammer 攻击利用这种降低的可靠性来诱导内存中的位翻转,而无需直接访问这些位。大多数 Rowhammer 攻击都以软件完整性为目标,但最近的一些攻击表明它可用于破坏机密性。延续这一趋势,我们在本文中观察到 Rowhammer 攻击与内存瞬时功耗密切相关。我们利用这一观察结果设计了 HammerScope,这是一种基于 Rowhammer 的攻击技术,用于测量内存单元的功耗。由于功耗与内存的活动水平相关,因此 HammerScope 允许攻击者推断内存活动。为了展示 HammerScope 的攻击能力,我们使用它发起了三次信息泄露攻击。我们首先展示 HammerScope 可用于破坏内核地址空间布局随机化 (KASLR)。我们的第二次攻击使用内存活动作为 Spectre 攻击的隐蔽通道,使我们能够从操作系统内核泄露信息。最后,我们演示了如何使用 HammerScope 进行网站指纹识别,从而危及用户隐私。我们的工作证明了找到 Rowhammer 攻击的系统解决方案的重要性。

超低功耗边缘 AI 模块 Type2DA

1. 启动 Tera Term 并选择 USB Serial Port 2. 将串口设置为 115200,然后按下 AI Reset 按钮(下图中位置‘ 〇 ’)。 3. 发出“UP”的声音以确认识别