XiaoMi-AI文件搜索系统

World File Search System2014 年第 37 届国际信息与... 会议

2014 年第 37 届信息和通信技术、电子学和微电子学国际大会(MIPRO) 微电子学、电子学和电子技术纳米技术,从近代历史到(不)可预测的未来 - 特邀论文 1 J. Turkovic 基于低温(α)和高温(β)GeS 2 晶相的簇共存的光谱证据,位于玻璃状二硫化锗基质中 7 V. Mitsa、R. Holomb、G. Lovas、M. Veres、M. Ivanda、T. Kovach 银胶体纳米粒子的合成和表征及其在表面增强拉曼光谱中的应用 11 L. Mikac、M. Ivanda、M. Gotic、T. Mihelj 碲酸盐玻璃的拉曼光谱 15 H. Gebavi、D. Ristic、V. Djerek、L. Mikec、M. Ivanda、D.用于尖端光子学应用的米兰涂层球形微谐振器 18 D. Ristic、M. Mazzola、A. Chiappini、C. Armellini、A. Rasoloniaina、P. Féron、R. Ramponi、G.N.Conti、S. Pelli、G.C.Righini、G. Cibiel、M. Ivanda、M. Ferrari 使用 THz 时域光谱检查硅材料特性 22 B. Pejcinovic 微带宽度和退火时间对微尺度石墨烯 FET 特性的影响 27 M. Poljak、M. Wang、S. Zonja、V. Djerek、M. Ivanda、K.L.Wang, T. Suligoj 具有优化发射极和电介质的石墨烯基晶体管 33 S. Venica, F. Driussi, P. Palestri, L. Selmi 厚度低于 20 nm 的双栅极锗 MOSFET 中受声子限制的空穴迁移率 39 V. Ivanic, M. Poljak, T. Suligoj 20 nm 栅极体和 SOI FinFET 之间的 RF 性能比较 45 S. Krivec, H. Prgic, M. Poljak, T. Suligoj CMOS 二进制加法器老化的模拟研究 51 T. An, C. Hao, L. Alves de Barros Naviner 多故障下并发检查电路可靠性评估的分析方法 56 T. An, K. Liu, L. Alves de Barros Naviner CMOS 乘法器结构的合成使用多功能电路 60 C. Popa

量子计算接口的 VLSI 架构 - ijrpr

量子计算利用叠加和纠缠的原理,允许量子比特或量子位同时存在于多个状态中。这一特性使量子计算机能够以比传统计算机快得多的速度处理特定任务的数据,包括分解大数和解决复杂的优化问题。量子霸权的前景促使全球开展大量研究和开发工作,企业和研究机构竞相构建现实的量子处理器。尽管量子计算具有巨大的潜力,但要在现实应用中实现其优势仍需要克服艰巨的挑战。最大的障碍之一在于建立量子和经典结构之间的持续接口。量子处理器在敏感的量子王国中运行,必须与经典加法器进行通信,而不会损害量子数据的完整性。这种复杂的交互需要一种先进的 VLSI 架构,能够促进有效通信、最大限度地减少错误并优化量子-经典混合系统的整体性能。在量子计算接口的背景下混合 VLSI 需要摆脱传统策略。经典计算机遵循确定性原则,而量子结构则以概率方式运行,引入不确定性并要求同步条件。由于量子处理器产生具有固有概率不确定性的结果,VLSI 结构必须提供纠错机制和容错设计,以保持量子计算的可靠性。此外,经典和量子处理器之间的工作条件差异带来了额外的复杂性。量子处理器通常在极低的温度下工作以保持敏感量子态,而经典组件则在室温下工作。设计 VLSI 架构以促进绿色通信和跨这些温度梯度的数据传输需要创新的工程解决方案。在开发用于量子计算接口的 VLSI 架构的过程中,研究人员正在努力设计可扩展和模块化结构。量子处理器面临可扩展性挑战的风险,而 VLSI 在解决这些问题方面发挥着关键作用。可扩展架构的开发对于了解量子计算在解决实际问题方面的全部能力至关重要。尽管存在这些挑战,但目前量子计算接口 VLSI 架构的改进已取得显著进展。研究人员探索了各种策略,从集成到经典系统中的专用量子协处理器,到利用经典处理器完成精确任务同时将量子计算委托给专用处理器的混合架构。这些努力聚焦于不断发展的量子经典集成全景,其中 VLSI 架构是实现绿色和可扩展解决方案的关键。

电子产品

单元 1:放大器 16 小时 多级放大器:多级放大器的需求和使用、总增益、级联与共源共栅。RC 耦合放大器。达林顿放大器 - 电路、电流增益、Zi、Zo、优点。功率放大器:电压与功率放大器、功率放大器的需求、分类 A 类、C 类(仅提及)B 类:推挽放大器、工作、效率(推导)、交叉失真、谐波失真、互补对称(无变压器)。比较。调谐放大器:需要单调谐和双调谐、工作、频率响应曲线、优点和缺点、耦合说明。JFET - 类型 - p 沟道和 n 沟道、工作和 IV 特性 - n 沟道 JFET、参数及其关系、BJT 和 JFET 的比较。共源放大器、MOSFET:E&D、MOSFET – n 沟道和 p 沟道、构造、工作、符号、偏置、漏极和传输特性、CMOS 逻辑、CMOS 反相器 - 电路、工作和特性。单元 2:反馈放大器和振荡器 10 小时反馈:反馈类型正反馈和负反馈、框图、反馈对 Av、BW、Zi 和 Zo 的影响(仅适用于电压串联反馈放大器电路)。振荡器的需求;正反馈、储能电路 – 振荡、谐振频率。巴克豪森振荡准则、LC 调谐振荡器 - Colpitts 和 Hartley 振荡器、振荡频率(无推导)、最小增益、优点和缺点、RC 振荡器 - 相移和 Wein 桥振荡器(无推导)、频率和最小增益、晶体振荡器、压电效应、等效电路、串联和并联谐振电路、Q 因子。非正弦振荡器:非稳态多谐振荡器,工作波形,频率公式(仅提及),单稳态多谐振荡器,双稳态多谐振荡器(触发器概念)。 单元 3:集成电路 04 小时 IC555 框图和引脚图。 IC555 应用 - 非稳态(推导)和单稳态多谐振荡器,压控振荡器。 施密特触发器。 IC 稳压器:LM317,IC78XX,79XX 系列(框图) 单元 4:运算放大器(Op-Amp) - 理论与应用 11 小时 Op-Amp 框图,引脚图 IC741,规格,理想和实际运算放大器参数的特性 - 输入偏置电流,输入失调电压,输出失调电压,CMRR,斜率 SVRR,失调零,开环运算放大器限制,闭环运算放大器。负串联反馈放大器的框图,反相和非反相反馈电路,增益,R if ,R of 。虚拟接地,单位增益带宽积。应用:加法器 - 反相和非反相,减法器,比例变换器,缓冲器,积分器,微分器(理想和实用)。比较器,过零检测器,有源滤波器 - 巴特沃斯一阶低通、高通、带通、带阻、全通滤波器。二阶滤波器(仅提及)。自学:04 小时 IC 制造技术。推荐教科书 1、运算放大器和线性电路,Ramakanth Gayakwad PHI,第 5 版,2015 年。2. 应用电子学教科书,RS Sedha

6T 1位全加器的实现与分析

VI. 参考文献 [1] DanWang, Maofeng & Wucheng,“180nm CMOS 技术中的新型低功耗全加器单元”,DOI:10.1109/ICIEA.2009.5138242,工业电子与应用,2009 年。ICIEA 2000。第四届 IEEE 会议,2009 年 6 月。 [2] Kamlesh Kukreti、Prashant Kumar 等人,“基于多米诺逻辑技术的全加器性能分析”,DOI:10.1109/ICICT50816.2021.9358544,印度哥印拜陀,2021 年。 [3] Umapathi.N、Murali Krishna、G. Lingala Srinivas。 (2021)“对进位选择加法器独特实现的综合调查”,IEEE 和 IAS 第四届两年一度的新兴工程技术国际会议,于 1 月 15 日至 16 日在印度新孟买举行。[4] Subodh Wairya、Rajendra Kumar 等人,“用于低压 VLSI 设计的高速混合 CMOS 全加器电路性能分析”,DOI:10.1155/2012/173079,2012 年 4 月。[5] N. Umapathi、G.Lavanya (2020)。使用 Dadda 算法和优化全加器设计和实现低功耗 16X16 乘法器。国际先进科学技术杂志,29(3),918-926。[6] Pankaj Kumar、Poonam Yadav 等人,“基于 GDI 的低功耗应用全加器电路设计和分析”,国际工程研究与应用杂志,ISSN:2248-9622,第 4 卷,第 3 期(第 1 版),2014 年 3 月。[7] NM Chore 和 RNMandavgane,“低功耗高速一位全加器调查”,2010 年 1 月。[8] Gangadhar Reddy Ramireddy 和 Yashpal Singh,“亚微米技术下拟议的全加器性能分析”,国际现代科学技术趋势杂志第 03 卷,第 03 期,2017 年 3 月 ISSN:2455-3778。 [9] Chandran Venkatesan、Sulthana M.Thabsera 等人,“使用 Cadence 45nm 技术的不同技术分析 1 位全加器”,DOI:10.1109/ICACCS.2019.8728449,2019 年 3 月,印度哥印拜陀。[10] K.Dhanunjaya、Dr.MN.Giri Prasad 和 Dr.K.Padmaraju,“使用 45nm Cmos 技术的低功耗全加器单元性能分析”,国际微电子工程杂志(IJME),第 3 卷。 1,No.1,2015 年。[11] Karthik Reddy.G,“Cadence Virtuoso 平台中 1 位全加器的低功耗面积设计”,国际 VLSI 设计与通信系统杂志 (VLSICS) 第 4 卷,第 4 期,2013 年 8 月,DOI:10.5121/vlsic.2013.4406 55。[12] Kavita Khare 和 Krishna Dayal Shukla,“使用 Cadence 工具设计 1 位低功耗全加器”,引用为:AIP 会议论文集 1324,373 (2010),2010 年 12 月 3 日。[13] Murali Krishna G. Karthick、Umapathi N.(2021)“低功耗高速应用的动态比较器设计”。引自:Kumar A.、Mozar S. (eds) ICCCE 2020。电气工程讲义,第 698 卷。Springer,新加坡。[14] Murali Anumothu、BRChaitanya Raju 等人“使用基于多路复用器的 GDI 逻辑设计和分析 45nm 技术中的 1 位全加器的性能”,第 3 卷(2016),第 3 期,2016 年 3 月。[15] Partha Bhattacharyya、Bijoy Kundu 等人。al“低功耗高速混合 1 位全加器电路的性能分析”,第 23 卷,第 10 期,DOI:10.1109/TVLSI.2014.2357057,2015 年 10 月。

分布式量子门的通用协议

实践中,需要大规模量子计算机来以更高的速度解决复杂问题,但在实现上存在一些问题,如量子退相干。其原因是量子比特与环境相互作用,从而对误差更敏感[10-12]。解决上述问题的一个合理方法是使用分布式量子计算机减少处理信息时使用的量子比特数量。分布式量子计算机可以由两个或多个具有较少量子比特的低容量量子计算机构建,类似于用于解决单个问题的量子系统网络中的分布式节点或子系统[13,14]。在这种结构中,需要量子(经典)通信协议来在单独的节点之间进行通信。分布式量子计算最早由 Grover [15]、Cleve 和 Buhrman [16] 以及 Cirac 等人 [17] 提出。随后,Ying和Feng [11]定义了一种描述分布式量子电路的代数语言。之后,Van Meter等[18]提出了分布式量子电路中的VBE进位波加法器结构。与此同时,该领域的一些工作集中在通信部分。2001年,Yepez [19]提出了两种类型的量子计算机。在第I类量子计算机中,量子通信用于互连分布式量子计算机的子系统。在II类量子计算机中,使用经典通信代替量子通信来互连分布式量子计算机的子系统或节点。在量子通信中,在网络节点之间传输量子比特的著名方法之一是量子隐形传态(QT)[20–23]。在隐形传态中,量子比特在两个用户或节点之间传输,而无需物理移动它们。然后,在量子比特上本地执行计算;这种方法也称为远程数据。还有一些工作侧重于优化分布式量子电路的通信成本。假设量子比特隐形传态是一种昂贵的资源,这类工作试图减少这种远程数据 [ 24 – 26 ]。在 [24 ] 中,作者考虑了具有公共控制或目标量子比特的连续 CNOT 门。他们表明,这样的结构只需一次隐形传态即可执行两个门。在 [25 ] 和 [26 ] 中,这个想法得到了扩展,并提出了一些算法来减少所需的隐形传态次数。考虑了所有可能导致通信减少的配置。[27 – 29 ] 还分别考虑了使用启发式方法、动态规划方法和进化算法来优化隐形传态次数。另一种方法称为远程门,当节点相距甚远时,它使用量子纠缠直接远程执行门。远程门方法的挑战之一是在位于分布式量子计算机不同节点的量子比特之间建立 n 量子比特控制量子门的最佳实现。根据所考虑的库(如 NCV、NCT、Clifford + T 等),可以使用不同的控制门来合成量子电路的变换矩阵。众所周知的可逆量子门之一是 Toffoli 门。Toffoli 门与 Hadamard 门一起构成了量子计算的通用集。此外,具有两个以上控制量子比特的多控制 Toffoli 门在量子计算中得到广泛应用。因此,实现在网络的不同节点之间应用 n 量子比特远程 Toffoli 门(受控非门)的协议至关重要。

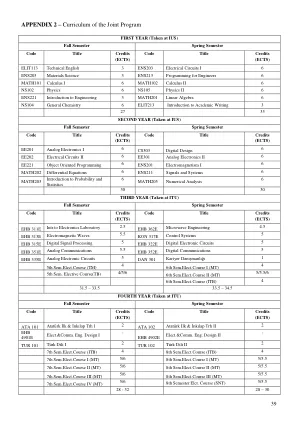

IUS 2025春季课程计划本科

ITU至少有30天的实习是强制性的。课程目录描述在IUS:CS303数字设计:关于数字电子构建块的标准入门课程。学生将学习布尔代数的公理,数字系统和表示,逻辑门的功能,编码器,解码器,多路复用器,分流器,加法器,减法器,触发器等。课程包括简单有限状态机的分析和设计。简要研究了不同电路家族的物理实施以及数字记忆的体系结构。学生还将学习使用VHDL在可编程逻辑设备中实现数字电路。EE201模拟电子I:传导。半导体,载体,P型和-Type掺杂,漂移和扩散机制,PN连接的物理结构和行为。理想二极管,实用二极管,电气行为和电流 - 电压曲线。二极管模型。DC分析方法的二极管电路(恒定电压下降模型,带指数模型的固定点迭代)。小信号近似,二极管小信号等效和二极管电路的交流分析,直流电源设计(整流器,用滤波器电容器对拓扑分析)。Zener二极管和调节。身体耐药性和寄生能力。其他二极管类型。双极结构晶体管(BJT),早期现象,BJT操作区域,电气模型(Ebers-Moll)和特征的物理结构和行为。DC偏置和BJT电路的热稳定性。MOSFET,操作区域,特征,重要次要效应(通道长度调制,身体效应)的物理结构和行为。DC偏置和MOSFET电路的热稳定性。切换BJT和MOSFET的应用,这是数字电路中的概念用法。EE202电路II:高阶动态电路的状态和输出方程。状态过渡矩阵和属性。zerostate,零输入和总响应。正弦稳态。在JW-域中找到动态网络和系统的状态和输出方程。拟态。力量。三相系统。在S域中找到动态网络和系统的状态和输出方程。阻抗和入学。稳定性和劳斯标准。网络功能和参数。块和信号流程图。bode图。ee221面向对象的编程:数据类型,控制语句,循环,阵列,功能,指针,动态内存,抽象和封装,类,对象,构造函数,构造函数和驱动器,继承和多态性,类,类等级,超级类,超级类,亚类,互动类,界面,界面,界面,界面,虚拟方法,虚拟方法,operator,Operator opertranting,Operator,Operator opertranting。EE301模拟电子II:扩增和增益概念,Desibell概念,电压放大器 /电流放大器 /跨导电电路 /跨逆性电路模型,晶体管在扩增中的概念功能。DC分析晶体管(BJT,MOSFET)电路。BJT和MOSFET的小信号当量和末端电阻。AC分析BJT和MOSFET放大器:基本放大器阶段的增益和输入/输入电阻,分析级联(直接/电容性耦合)放大器。cascode结构,达灵顿结构。差分放大器,差分和共同模式增益,共同模式排斥比。当前来源,负载的电路。操作放大器,理想和实际行为,样品操作机的内部结构。opamp的线性和非线性应用,非理想性对行为的影响。功率放大器。eens221工程学简介:本课程是工程学深度一年级学生的方向课程。它旨在使学生适应更轻松,并告知他们有关电子产品的一般主题以及电信工程,工程道德和质量。各种教职员工向学生们发表演讲。提供了申请的示例,加上工程伦理守则,道德责任,设计中的质量问题和应用程序。ELIT113技术英语:本课程旨在通过使用引起的信息通过阅读和分析技术和学术文本以及学术和技术写作技巧来提高学生的阅读能力。学生不仅了解学术和技术英语的要求,还可以提高他们的其他语言和批判性思维能力。ELIT213学术写作简介:旨在教授组织和关键的课程学生有望通过使用适当的技术语言来广泛描述对象和机制,以对他们所研究的信息进行分类并撰写有关分类的分析组成,以引用他们在整个过程中使用的所有信息。