XiaoMi-AI文件搜索系统

World File Search System容错计算:基本概念

在最低层次上,故障与技术有关。金属或多晶硅信号线的短路或开路等物理缺陷会改变电压、开关时间和其他特性。3 外部干扰也在这个层次上起作用,影响信号线、电荷存储和其他特性。在逻辑层次上,数字系统由门和存储元件建模,所有信号都表示为二进制值。低级容错策略旨在检测或屏蔽产生错误逻辑值的故障。由于其简单性,“卡住”模型是最广泛使用的逻辑故障模型,该模型假设故障在信号线上表现为固定的逻辑值。更复杂的模型是“桥接”故障,其中信号线之间的耦合导致一条线的逻辑值影响另一条线的值。其他复杂故障会改变门的基本逻辑功能,这在可编程逻辑阵列中经常发生,其中 AND/OR 阵列中连接的存在或不存在会导致功能中添加或删除蕴涵项。在更高的抽象级别(寄存器、算术逻辑单元、处理器等)中,故障通常表现为模块行为的变化,由其真值表或状态表表示。在此级别,故障建模通常更抽象,以方便在行为级别进行模拟;因此,通常会牺牲准确性。

容错计算:基本概念

在最低层次上,故障与技术有关。金属或多晶硅信号线的短路或开路等物理缺陷会改变电压、开关时间和其他特性。3 外部干扰也在这个层次上起作用,影响信号线、电荷存储和其他特性。在逻辑层次上,数字系统由门和存储元件建模,所有信号都表示为二进制值。低级容错策略旨在检测或屏蔽产生错误逻辑值的故障。由于其简单性,“卡住”模型是最广泛使用的逻辑故障模型,该模型假设故障在信号线上表现为固定的逻辑值。更复杂的模型是“桥接”故障,其中信号线之间的耦合导致一条线的逻辑值影响另一条线的值。其他复杂故障会改变门的基本逻辑功能,这在可编程逻辑阵列中经常发生,其中 AND/OR 阵列中连接的存在或不存在会导致功能中添加或删除蕴涵项。在更高的抽象级别(寄存器、算术逻辑单元、处理器等)中,故障通常表现为模块行为的变化,由其真值表或状态表表示。在此级别,故障建模通常更抽象,以方便在行为级别进行模拟;因此,通常会牺牲准确性。

容错计算:基本概念

在最低层次上,故障与技术有关。金属或多晶硅信号线的短路或开路等物理缺陷会改变电压、开关时间和其他特性。3 外部干扰也在这个层次上起作用,影响信号线、电荷存储和其他特性。在逻辑层次上,数字系统由门和存储元件建模,所有信号都表示为二进制值。低级容错策略旨在检测或屏蔽产生错误逻辑值的故障。由于其简单性,“卡住”模型是最广泛使用的逻辑故障模型,该模型假设故障在信号线上表现为固定的逻辑值。更复杂的模型是“桥接”故障,其中信号线之间的耦合导致一条线的逻辑值影响另一条线的值。其他复杂故障会改变门的基本逻辑功能,这在可编程逻辑阵列中经常发生,其中 AND/OR 阵列中连接的存在或不存在会导致功能中添加或删除蕴涵项。在更高的抽象级别(寄存器、算术逻辑单元、处理器等)中,故障通常表现为模块行为的变化,由其真值表或状态表表示。在此级别,故障建模通常更抽象,以方便在行为级别进行模拟;因此,通常会牺牲准确性。

容错计算:基本概念

最低级别,故障与技术有关。金属或多晶硅信号线中的短路或开路等物理缺陷会改变电压、开关时间和其他属性。3 外部干扰也在这个级别起作用,影响信号线、电荷存储和其他属性。在逻辑级别,数字系统由门和存储元件建模,所有信号都表示为二进制值。低级容错策略旨在检测或屏蔽产生错误逻辑值的故障。由于其简单性,“卡住”模型是最广泛使用的逻辑故障模型,假设故障在信号线上表现为固定的逻辑值。更复杂的模型是“桥接”故障,其中信号线之间的耦合导致一条线的逻辑值影响另一条线的值。其他复杂故障会改变门的基本逻辑功能,这在可编程逻辑阵列中经常发生,其中 AND/OR 阵列中连接的存在或不存在会导致在功能中添加或删除蕴涵项。在更高的抽象级别(寄存器、算术逻辑单元、处理器等)故障通常表现为模块行为的变化,由其真值表或状态表表示。在此级别,故障建模通常更抽象,以方便在行为级别进行模拟;因此,通常会牺牲准确性。

容错计算:基本概念

在最低层次上,故障与技术有关。金属或多晶硅信号线的短路或开路等物理缺陷会改变电压、开关时间和其他特性。3 外部干扰也在这个层次上起作用,影响信号线、电荷存储和其他特性。在逻辑层次上,数字系统由门和存储元件建模,所有信号都表示为二进制值。低级容错策略旨在检测或屏蔽产生错误逻辑值的故障。由于其简单性,“卡住”模型是最广泛使用的逻辑故障模型,该模型假设故障在信号线上表现为固定的逻辑值。更复杂的模型是“桥接”故障,其中信号线之间的耦合导致一条线的逻辑值影响另一条线的值。其他复杂故障会改变门的基本逻辑功能,这在可编程逻辑阵列中经常发生,其中 AND/OR 阵列中连接的存在或不存在会导致功能中添加或删除蕴涵项。在更高的抽象级别(寄存器、算术逻辑单元、处理器等)中,故障通常表现为模块行为的变化,由其真值表或状态表表示。在此级别,故障建模通常更抽象,以方便在行为级别进行模拟;因此,通常会牺牲准确性。

7.4 容错计算 7.4.1 窃密代码或7量子比特……

到目前为止,我们已经介绍了规范化器 { ˆ XL , ˆ ZL , ˆ HL , ˆ SL , CNOT L } 的情况,即所谓的 Cli↵ord 群。值得注意的是,Gottesman-Knill 定理表明,仅使用该群元素执行的操作可以用经典方式模拟。因此,人们无法在量子上超越经典计算机。此外,Cli↵ord 群不是通用的,这意味着该群元素的组合不足以实现任意门。这本质上是 Solovay-Kitaev 定理的论证。需要扩展 Cli↵ord 群,添加至少一个不属于该群的额外门。这可以是 T 门或 To↵oli 门。

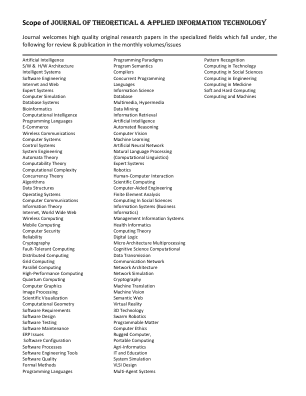

《理论与应用信息技术》期刊范围

人工智能 软件和硬件架构 智能系统 软件工程 互联网和网络 专家系统 计算机模拟 数据库系统 生物信息学 计算智能 编程语言 电子商务 无线通信 计算机系统 控制系统 系统工程 自动机理论 可计算性理论 计算复杂性 并发性理论 算法 数据结构 操作系统 计算机通信 信息理论 互联网、万维网 无线计算 移动计算 计算机安全 可靠性 密码学 容错计算 分布式计算 网格计算 并行计算 高性能计算 量子计算 计算机图形学 图像处理 科学可视化 计算几何 软件需求 软件设计 软件测试 软件维护 ERP 问题 软件配置 软件流程 软件工程工具 软件质量 形式化方法 编程语言

BYU ScholarsArchive 引文 BYU ScholarsArchive 引文 Bunker, Robert L. (1994) “利阿贺拿的设计与第二主轴的目的”,《摩尔门经研究期刊》:第 3 卷:第 2 期,第 1 篇文章。可从以下网址获取:https://scholarsarchive.byu.edu/jbms/vol3/iss2/1

利阿贺拿是主赐给李海的通讯设备,用来决定正确的行进方向。这个设备有两个指针,只有一个指针是必要的,用来提供方向信息。但利阿贺拿的功能不只是一个简单的指南针,因为它还需要信心才能正确操作。由于一个指针总是“指向”某个方向,所以需要额外的指针来指示第一个指针是否可以依赖。第二个指针的这个拟议用途符合现代容错计算机系统中一种成熟的工程原理,称为“投票”,其中比较两个相同的过程状态,如果它们相同,则宣布正确,如果它们不同,则宣布不正确。因此,当第二个指针与第一个指针重合时,表示操作正确,而当它们正交时,表示未操作。

BYU ScholarsArchive 引文 BYU ScholarsArchive 引文 Bunker, Robert L. (1994) “利阿贺拿的设计和第二主轴的目的”,《摩尔门经研究杂志》:第 3 卷:第 2 期,第 1 篇文章。可从以下网址获取:https://scholarsarchive.byu.edu/jbms/vol3/iss2/1

利阿贺拿是主赐予利希的通讯设备,用于确定适当的行进方向。该设备包含两个指针,其中只有一个指针是提供方向信息的必需指针。但利阿贺拿的功能不仅仅是一个简单的指南针,因为它还需要信念才能正确操作。由于单个指针始终“指向”某个方向,因此需要额外的指针来指示是否可以依赖第一个指针。第二个指针的拟议用途符合现代容错计算机系统中使用的完善的工程原理,称为“投票”,其中比较两个相同的过程状态,如果它们相同,则宣布正确,如果它们不同,则宣布不正确。因此,当第二个指针与第一个指针重合时,表示操作正确,而当第二个指针正交时,表示非操作。