机构名称:

¥ 1.0

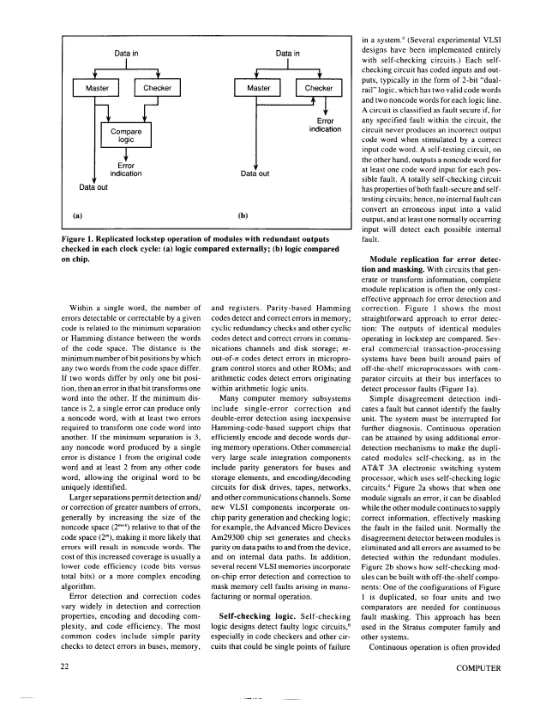

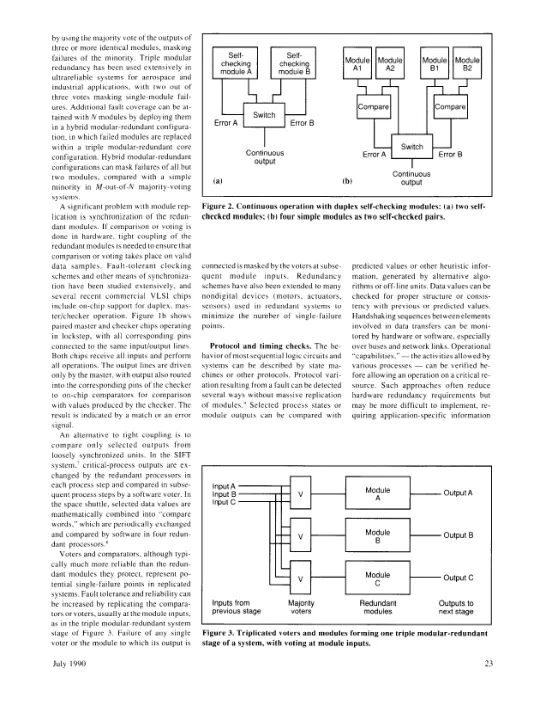

在最低层次上,故障与技术有关。金属或多晶硅信号线的短路或开路等物理缺陷会改变电压、开关时间和其他特性。3 外部干扰也在这个层次上起作用,影响信号线、电荷存储和其他特性。在逻辑层次上,数字系统由门和存储元件建模,所有信号都表示为二进制值。低级容错策略旨在检测或屏蔽产生错误逻辑值的故障。由于其简单性,“卡住”模型是最广泛使用的逻辑故障模型,该模型假设故障在信号线上表现为固定的逻辑值。更复杂的模型是“桥接”故障,其中信号线之间的耦合导致一条线的逻辑值影响另一条线的值。其他复杂故障会改变门的基本逻辑功能,这在可编程逻辑阵列中经常发生,其中 AND/OR 阵列中连接的存在或不存在会导致功能中添加或删除蕴涵项。在更高的抽象级别(寄存器、算术逻辑单元、处理器等)中,故障通常表现为模块行为的变化,由其真值表或状态表表示。在此级别,故障建模通常更抽象,以方便在行为级别进行模拟;因此,通常会牺牲准确性。

容错计算:基本概念

主要关键词