XiaoMi-AI文件搜索系统

World File Search System基于 ReRAM 的非易失性和抗辐射锁存器设计

摘要:在航空航天环境中,芯片的高可靠性和低功耗至关重要。为了大幅降低功耗,芯片的锁存器需要进入掉电操作。在此操作中,采用非易失性(NV)锁存器可以保留电路状态。此外,在航空航天环境中,锁存器可能会被辐射粒子击中,在最坏的情况下会导致严重的软错误。本文提出了一种基于电阻式随机存取存储器(ReRAM)的NV锁存器,用于NV和鲁棒应用。所提出的NV锁存器具有低开销的抗辐射能力,并且可以在掉电操作后恢复值。仿真结果表明,所提出的NV锁存器可以完全提供针对单粒子翻转(SEU)的抗辐射能力,并可以在掉电操作后恢复值。与其他类似解决方案相比,所提出的NV锁存器可以将存储单元中的晶体管数量平均减少50%。

基于标准单元的栅极尺寸和晶体管堆叠的抗辐射效率

近年来,晶体管技术的进步使得人们能够设计出越来越复杂的集成电路。随着在降低功耗和提高性能方面取得的巨大成就,在考虑深度扩展技术时也面临着新的挑战。明显的工艺变异性、老化和辐射效应是经常出现的设计挑战,其重要性也日益增加 [1-5]。集成电路越来越容易受到单个高能粒子撞击的影响,可能会产生破坏性或非破坏性的影响。当粒子撞击触发 CMOS 电路中固有的 PNPN 结构中的寄生晶体管时,就会发生单粒子闩锁 (SEL),这可能会产生破坏性影响 [6]。当高能粒子从顺序逻辑元件撞击晶体管的敏感区域并沉积足够的电荷以扰乱电路时,单粒子翻转 (SEU) 会以位翻转的形式出现。此外,组合逻辑电路容易受到单粒子瞬态 (SET) 效应的影响,这种效应表现为粒子与处于关断状态的晶体管漏极电极相互作用产生的寄生瞬态电流。这并不是单粒子效应 (SEE) 的详尽列表 [7]。辐射加固设计 (RHBD) 技术已经开发出来,用于应对不同辐射条件下电子电路的辐射效应

全耗尽硅中的抗辐射混合信号 IP 核

摘要 Global Foundries 的 22FDX 技术是一种商业化的尖端集成电路制造工艺。该工艺结合了 22 nm 的典型最小栅极长度和 FD-SOI(全耗尽绝缘体上硅)多层结构。这些技术特性允许自适应体偏置、超低电压供电和超低泄漏,从电路应用的角度来看,这些特性有利于节能的射频信号传输、高性能计算和强大的 MRAM(磁阻随机存取存储器)。因此,该技术非常适合克服当前用于高速和低功耗 AMS(模拟和混合信号)应用的产品解决方案。特别是,SOI 技术特性可确保免受单粒子闩锁的影响。

极地设计公司为太空应用设计了抗辐射 14T SRAM 单元

摘要 本文提出了一种用于航天应用的抗辐射极性设计 14T (RHPD-14T) SRAM 单元。通过估算 65 纳米互补金属氧化物半导体 (CMOS) 技术的各种设计指标,分析了所提出的 RHPD-14T 单元的性能。基于结合抗辐射极性设计技术与合理的布局拓扑,所提出的 RHPD-14T 可以耐受所有单节点翻转和部分双节点翻转。仿真结果表明,RHPD-14T 的写入访问时间比 RSP-14T/QUCCE-10T/DICE/S4P8N/We-Quatro(@VDD=1.2V) 短 1.83 倍 / 1.59 倍 / 1.56 倍 / 1.12 倍 / 1.05 倍。 RHPD-14T的字线写触发电压比QUCCE-10T/DICE/We-Quatro/S4P8N/RSP-14T (@VDD=1.2V)高2.67×/2.22×/1.35×/1.29×/1.26×;RHPD-14T的保持静态噪声容限比DICE/S4P8N/RHPD-12T (@VDD=1.2 V)高14.85×/7.15×/1.05×。此外,蒙特卡洛(MC)模拟证明RHPD-14T波动性小、稳定性强、恢复能力稳定、抗单效应翻转(SEU)能力强。关键词:保持静态噪声容限、极性设计抗辐射、单效应翻转分类:集成电路

熔盐反应堆中阿尔法探测器的抗辐射电子设备的考虑

本报告是由美国政府某个机构资助的工作报告。美国政府、其任何机构及其任何雇员均不对所披露的任何信息、设备、产品或流程的准确性、完整性或实用性做任何明示或暗示的保证,或承担任何法律责任或义务,亦不保证其使用不会侵犯私有权利。本文以商品名、商标、制造商或其他方式提及任何特定的商业产品、流程或服务,并不一定构成或暗示美国政府或其任何机构对其的认可、推荐或偏爱。本文表达的作者的观点和意见不一定表明或反映美国政府或其任何机构的观点和意见。

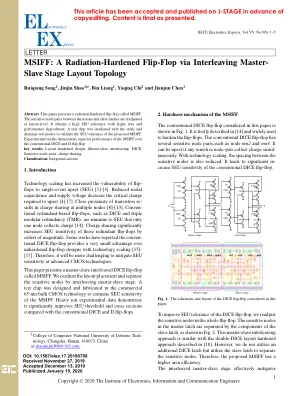

信件 MSIFF:通过交错主从级布局拓扑实现抗辐射触发器

敏感节点对之间的电荷共享。当入射离子撞击敏感晶体管(例如节点 mn2 中的 PMOS 晶体管)时,一列电子-空穴对会沿入射轨道电离。电离载流子扩散到相邻的晶体管,导致相邻敏感节点之间的电荷收集,如图 3 所示。对于传统的 DICE 触发器,敏感节点对将收集足够的电荷并导致 SEU。对于所提出的 MSIFF,增加的节点间距可有效减少由于复合过程引起的扩散收集。此外,从属锁存器的插入组件也有助于收集额外的载流子 [19]。它将显著降低电离载流子密度并阻止扩散收集过程。因此,敏感节点对不会同时收集足够的电荷,并且所提出的 MSIFF 中不会发生 SEU。

钙钛矿太阳能电池在太空应用中的抗辐射和强化策略的进展

金属卤化物钙钛矿 (MHP) 是一种具有优异性能的半导体材料,广泛应用于各个行业。这些材料通常表现出直接跃迁半导体行为,其特点是吸收系数高、激子结合能低,从而具有出色的 PV 性能。此外,MHP 显示出高效的载流子传输速率、较长的载流子寿命和显著的扩散长度,从而能够以最少的复合实现电子和空穴的有效传输。1 利用 MHP 作为吸收层的钙钛矿太阳能电池 (PSC) 已成为第三代太阳能电池的典范。2009 年,Miyasaka 等人实现了 PSC 开发的一个重要里程碑。用钙钛矿取代染料敏化太阳能电池中的吸收材料,使光伏转换效率 (PCE) 达到 3.8%。2 从那时起,PSC 引起了广泛关注,其 PCE 经历了快速增长,如图所示。1(A)。3 – 9 目前,单结 PSC 已实现认证 PCE 26.14%,10 稳步接近 Shockley – Queisser 效率极限 33.7%。11

高可靠性业务 | 新空间 关于我们

Hi-Rel Power Solutions 军用密封混合 DC/DC 转换器 5W 至 120W,单路、双路、三路版本 航天抗辐射密封混合 DC/DC 转换器 5W 至 120W,单路、双路、三路版本,TID 100krad,SEE 82MeV MIL-PRF-38534 DLA 认证,提供 SMD 部件号 新型航天抗辐射密封混合 DC/DC 转换器 25W、40W,单路、双路版本,TID 高达 30krad,SEE 高达 60MeV EMI 滤波器与其密封混合 DC/DC 转换器相辅相成,提供一系列输入电压和封装 基于抗辐射和抗辐射 PCB 的 DC/DC 转换器,具有关键功能并根据客户要求量身定制,单路、双路、三路、四路、八路版本,输出功率 5W 至 400W,TID 100krad,看到 60MeV

N型衬底超快三维沟槽电极硅探测器的抗辐射性能

摘要:ATLAS 和 CMS 实验预测高亮度大型强子对撞机(HL-LHC)最内层像素探测器的辐射注量高达 1 × 10 16 1 MeV n eq /cm 2。辐射剂量的增加将导致探测器性能下降,例如漏电流和完全耗尽电压增加,信号和电荷收集效率降低,这意味着有必要开发用于甚高亮度对撞机的抗辐射半导体器件。在我们前期对超快三维沟槽电极硅探测器的研究中,通过模拟不同最小电离粒子(MIP)撞击位置下的感应瞬态电流,验证了从 30 ps 到 140 ps 的超快响应时间。本工作将利用专业软件有限元技术计算机辅助设计(TCAD)软件框架,模拟计算探测器在不同辐射剂量下的全耗尽电压、击穿电压、漏电流、电容、加权场和MIP感应瞬态电流(信号)。通过分析模拟结果,可以预测探测器在重辐射环境下的性能。像素探测器的制作将在中国科学院微电子研究所的CMOS工艺平台上进行,采用超纯高电阻率(高达10 4 ohm·cm)硅材料。