XiaoMi-AI文件搜索系统

World File Search System内容

后减薄是半导体制造中器件制造和先进封装的关键部分。当由于处理困难导致最终晶圆厚度变得非常薄(比如 <100µm)时,载体支撑晶圆减薄就具有吸引力。减薄后处理(沉积、化学机械抛光 [CMP]、键合等)也受益于刚性和热机械稳定的支撑结构。为了实现最终晶圆的非常低的总厚度变化 (TTV),载体晶圆和临时键合材料(通常是粘合剂层)都必须提供足够低的 TTV。载体晶圆还必须具有合适的热膨胀系数 (CTE)。在本文中,我们介绍了一种玻璃载体解决方案和临时键合方法,它们结合起来可实现低 TTV 晶圆减薄。使用直径 150mm 的单晶钽酸锂晶圆进行可行性演示,仅通过晶圆研磨即可减薄 5µm。

5G、AI 和 IoT 设备受益于最新的双层材料

先进晶圆级封装的一个重要方面是使用临时晶圆键合 (TWB) 材料和工艺,使部分处理过的晶圆即使在极高的温度和高真空条件下也能承受各种后续步骤。如果要求他们描述能够节省时间和金钱同时保持最佳性能的“理想” TWB 材料解决方案,许多制造商会要求使用可以在室温下应用和键合的材料,并且可以在热压键合 (TCB) 步骤中操作减薄晶圆时提供保护。这些材料还应具有足够的柔韧性,以支持不同的固化选项,同时保持设备功能的完整性。同时,材料应能够使用各种分离技术将减薄晶圆从载体上分离。

NIST 和 NQI 的更新

晶圆处理 湿法清洗 溶剂清洗 Piranha 溶液 RCA 清洗 光刻 离子注入 干法蚀刻 湿法蚀刻 等离子灰化 热处理 快速热退火 炉退火 热氧化 化学气相沉积 (CVD) 物理气相沉积 (PVD) 分子束外延 (MBE) 电化学沉积 (ECD) 化学机械平坦化 (CMP) 晶圆测试 晶圆背面研磨 芯片制备 晶圆安装 芯片切割 IC 封装 芯片附着 IC 键合 引线键合 热超声键合 倒装芯片 晶圆键合 胶带自动键合 (TAB) IC 封装 烘烤 电镀 激光打标 修整和成型 IC 测试

W2W 混合键合界面的可靠性研究

摘要 — 评估了 1 µm 间距晶圆对晶圆 (W2W) Cu/SiCN 混合键合界面的电气可靠性。使用控制 IV 方法获取 W2W 混合堆栈的击穿电压分布。假设幂律模型,对使用条件外推可确认使用寿命超过 10 年,当温度低于 175 ◦ C 时,幂律指数高于 10。发现沿 Cu/SiCN 混合键合界面的传导机制为 Poole-Frenkel 发射,能量势垒等于 0.95 eV。仅在温度高于 200 ◦ C 和场高于 1.5 MV/cm 时才能观察到移动铜,证实了该键合界面对铜漂移具有良好的稳定性。索引术语 — 晶圆对晶圆 (W2W) 键合、可靠性、电介质击穿、混合焊盘泄漏。

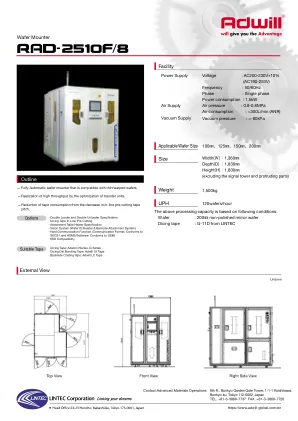

晶圆贴片机 - Adwill

双装载机和双卸载机规格 切割胶带在线预切割附件工作台加热器规格 视觉系统(晶圆 ID 阅读器和条形码附件系统) 主机通信功能(通信格式:符合 SECS-I 和 HSMS/软件:符合 GEM) ESD 兼容性

临时键合和解键合过程中的清洁和颗粒挑战

电话:707-628-5107 电子邮件:jbahena@veeco.com 摘要 5G、物联网和其他全球技术趋势的需求,加上缩小工艺节点成本的增加,已导致向更集成的封装要求转变。扇出晶圆级封装、2.5D/3D IC 封装和异构集成等先进封装技术的出现,为更小尺寸、更高功能和带宽带来了潜力。为了实现这些技术,通常需要对器件晶圆进行背面处理或减薄。这就要求使用临时粘合材料将器件晶圆粘附到刚性载体晶圆上,以便在处理和加工过程中提供机械支撑。释放载体后,必须彻底清除器件晶圆上的临时粘合材料。许多此类粘合剂都暴露在高功率激光或高温下,这使得清除更具挑战性。临时键合材料去除的亚微米级颗粒清洁要求也达到了通常为前端处理保留的标准。这在 3D 工艺中尤其重要,例如混合键合,其中特征和间距尺寸接近 < 1 µm,清洁不充分会导致后续键合工艺失败。因此,必须仔细考虑所有处理步骤以满足严格的颗粒要求。这项工作研究了硅晶片上涂层和烘烤的临时键合材料的去除,重点是获得最佳颗粒结果的加工条件。通过进行试样级研究和测量表面特性,在烧杯级评估了几种化学物质。根据这些发现,使用可定制的单晶圆加工工具对 300 毫米晶圆进行了研究。关键词临时键合材料、湿法清洗、晶圆级封装、单晶圆加工。I.简介 虽然晶体管和节点缩放一直在不断进步,但相关的成本和复杂性要求采用其他途径来提高性能。最突出的是,先进封装中的 2.5D/3D 集成通过将不同尺寸和材料的不同组件集成到单个设备中,显示出巨大的前景 [1]。由于许多当前的集成工艺流程都需要对设备晶圆进行背面处理或减薄,因此使用临时键合和脱键合 (TBDB) 系统已被证明是必要的多种类型的集成技术已经得到开发,例如扇出型晶圆级封装 (FOWLP)、2.5D 中介层、3D 硅通孔 (TSV) 和堆叠封装 (PoP),具有高集成度、低功耗、小型化和高可靠性等预期优势 [1-3]。

通孔-中间 TSV 晶圆混合键合中 Cu 突起对连接电阻的影响

摘要 本研究研究了铜突起对连接电阻的影响,作为中通孔硅通孔 (TSV) 晶片混合键合的详细数据。在制备了多个具有不同铜突起量的 Cu TSV 晶片和 Cu 电极晶片并通过表面活化键合方法使用超薄 Si 膜进行键合后,通过四端测量评估了键合晶片的连接电阻(即 TSV、Cu 电极和界面电阻之和)。结果表明,Cu 突起量是中通孔 TSV 晶片与超薄 Si 膜混合键合的关键参数,通过调节 Cu 突起可以在不进行热处理的情况下实现 TSV 和 Cu 电极之间的电连接。关键词 中通孔 硅通孔(TSV) 直接Si/Cu研磨 混合键合I.引言 随着摩尔定律的放缓,带有硅通孔(TSV)[1-6]的三维集成电路(3D-IC)已经成为实现高速、超紧凑和高功能电子系统的可行解决方案。3D-IC在某些电子系统中的接受度越来越高。然而,要将3D-IC技术应用于许多电子系统,需要进一步降低TSV形成成本、实现TSV小型化和提高TSV产量。在各种TSV形成工艺中,中通孔Cu-TSV工艺可以有效减小TSV尺寸并提高TSV产量,因为该工艺易于形成(1)小TSV,并且(2)TSV与多层互连之间的电接触。然而,如果晶圆背面露出的TSV高度变化很大,则可能会发生TSV断裂或接触失效。在之前的研究中,我们提出了一种 Cu-TSV 揭示工艺,包括直接 Si/Cu 研磨和残留金属去除 [7-9](图 1),以克服这一问题。首先,使用新型玻璃化砂轮进行直接 Si/Cu 研磨,并使用高压微射流 (HPMJ) 对砂轮进行原位清洁。由于非弹性

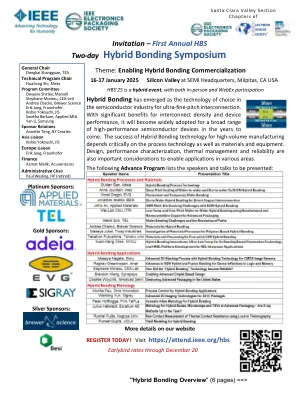

两天的混合键合研讨会

混合键合是一种用于堆叠两个结构的技术,例如芯片,晶圆和底物,每个结构都由金属和周围的介电材料组成。在混合键合过程之后,金属互相键合,并且介电材料也无缝连接。混合键合被认为是3D IC整合中的最终技术之一。但是,在混合键合的出现之前,首先引入了Cu-to-Cu键合,以实现3D IC集成的概念。在1999年至2002年之间,REIF在麻省理工学院的小组提出了一种晶圆级3D集成方案,其中包括使用处理晶片(Si Carrier晶片),研磨技术和Cu-to-to-Cu直接键合,如图1 [1]所示。要键合的Cu结构由Cu垫组成,类似于当今使用的Cu凸起和CU支柱。