XiaoMi-AI文件搜索系统

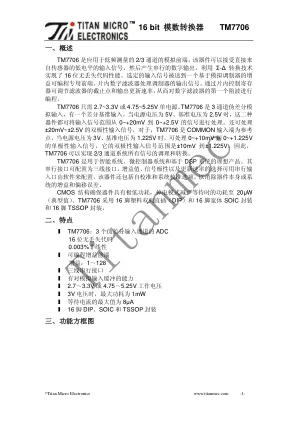

World File Search System16 bit 模数转换器TM7706 - NET

注释: 1.B 级温度范围为 -40 ℃ ~+85 ℃。 2.这些数据是按最初设计的产品发布的。 3.一次校准实际上是一次转换,因此这些误差就是表 1 和表 3 所示转换噪声的阶数。这 适用于在期望的温度下校准后。 4.任何温度条件下的重新校准将会除去这些漂移误差。 5.正满标度误差包括零标度误差 ( Zero-Scale Error )(单极性偏移误差或双极性零误 差),且既适用于单极性输入范围又适用于双极性输入范围。 6.满标度漂移包括零标度漂移 (单极性偏移漂移或双极性零漂移)且适用于单极性及 双极性输入范围。 7.增益误差不包括零标度误差,它被计算为满标度误差——对单极性范围为单极性偏移 误差,而对双极性范围为满标度误差——双极性零误差。 8.增益误差漂移不包括单极性偏移漂移和单极性零漂移。当只完成了零标度校准时,增 益误差实际上是器件的漂移量。 9.共模电压范围:模拟输入电压不超过 V DD +30mV ,不低于 GND-30mV 。电压低于 GND-200mV 时,器件功能有效,但在高温时漏电流将增加。 10.这里给出的 AIN ( + )端的模拟输入电压范围,对 TM7706 而言是指 COMMON 输入 端。输入模拟电压不应超过 V DD +30mV, 不应低于 GND-30mV 。 GND-200mV 的输入 电压也可采用,但高温时漏电流将增加。 11.VREF=REF IN ( + )- REF IN ( - )。 12.只有当加载一个 CMOS 负载时,这些逻辑输出电平才适用于 MCLK OUT 。 13.+25 ℃时测试样品,以保证一致性。 14.校准后,如果模拟输入超过正满标度 , 转换器将输出全 1, 如果模拟输入低于负满标度, 将输出全 0 。 15.在模拟输入端所加校准电压的极限不应超过 V DD +30mV 或负于 GND - 30mV 。 16.当用晶体或陶瓷谐振器作为器件的时钟源时 (通过 MCLK 引脚 ), V DD 电流和功耗 随晶体和谐振器的类型而变化 (见“时钟和振荡器电路”部分)。 17.在等待模式下,外部的主时钟继续运行, 5V 电压时等待电流增加到 150 μ A , 3V 电 压时增加到 75 μ A 。当用晶体或陶瓷谐振器作为器件的时钟源时,内部振荡器在等待 模式下继续运行,电源电流功耗随晶体和谐振器的类型而变化 (参看“等待模式” 一节)。 18.在直流状态测量,适用于选定的通频带。 50Hz 时, PSRR 超过 120dB (滤波器陷波 为 25Hz 或 50Hz )。 60Hz 时, PSRR 超过 120dB (滤波器陷波为 20Hz 或 60Hz )。 19.PSRR 由增益和 V DD 决定,如下:

模数转换器

我们力争走在 ADC 技术和开发战略的前沿。我们拥有 12 种内部发现的 ADC 候选药物,这证明了我们在 ADC 创新方面的实力,包括:(i) 六种临床阶段 ADC,具有广泛适应症的潜力,且具有未满足的医疗需求,根据 Frost & Sullivan 的数据,每种药物在整体或主要适应症开发进度方面均位居全球临床最先进的行列;(ii) 两种下一代双特异性 ADC(“BsADC”)和一种自身免疫 ADC,预计将于 2024 年至 2026 年进入临床阶段;以及 (iii) 多种其他临床前 ADC。我们的三种临床阶段产品,包括核心产品 DB-1303/BNT323 和 DB-1311/BNT324 以及关键产品 DB-1305/BNT325,已获得美国食品药品监督管理局(“ FDA ”)的快速通道认证,DB-1303 已获得 FDA 和国家药品监督管理局(“ NMPA ”)针对某些适应症的突破性治疗认证。DB-1303 是一种后期临床阶段 HER2 ADC 候选药物,目前有两项正在进行的注册试验和一项潜在的注册研究,第一项适应症(表达 HER2 的子宫内膜癌(“ EC ”)预计最早将于 2025 年向 FDA 提交加速批准申请。

在重复模式下使用 M16C/62 模数转换器

1. 本文档中包含的所有信息截至本文档发布之日均为最新信息。但是,此类信息如有更改,恕不另行通知。在购买或使用本文列出的任何瑞萨电子产品之前,请与瑞萨电子销售办事处确认最新产品信息。此外,请定期仔细关注瑞萨电子将披露的其他信息和不同信息,例如通过我们的网站披露的信息。 2. 对于因使用本文档中描述的瑞萨电子产品或技术信息而导致的或由此引起的第三方专利、版权或其他知识产权的侵权,瑞萨电子不承担任何责任。在此不授予瑞萨电子或其他方的任何专利、版权或其他知识产权的明示、暗示或其他形式的许可。 3. 您不得更改、修改、复制或以其他方式盗用任何瑞萨电子产品,无论是全部还是部分。 4. 本文档中提供的电路、软件和其他相关信息的描述仅用于说明半导体产品的操作和应用示例。您完全有责任将这些电路、软件和信息纳入您的设备设计中。瑞萨电子不承担您或第三方因使用这些电路而遭受的任何损失的责任,因此

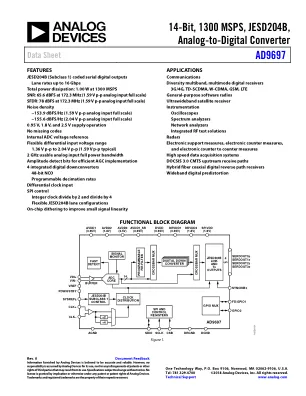

14 位、1300 MSPS、JESD204B 模数转换器

特性 JESD204B(子类 1)编码串行数字输出 通道速率高达 16 Gbps 总功耗:1300 MSPS 时为 1.00 W SNR:172.3 MHz 时为 65.6 dBFS(1.59 V p-p 模拟输入满量程) SFDR:172.3 MHz 时为 78 dBFS(1.59 V p-p 模拟输入满量程) 噪声密度 −153.9 dBFS/Hz(1.59 V p-p 模拟输入满量程) −155.6 dBFS/Hz(2.04 V p-p 模拟输入满量程) 0.95 V、1.8 V 和 2.5 V 电源操作 无丢失代码 内部 ADC 电压基准 灵活的差分输入电压范围 1.36 V p-p 至2.04 V p-p(典型值 1.59 V p-p) 2 GHz 可用模拟输入全功率带宽 幅度检测位,可实现高效的 AGC 实施 4 个集成数字下变频器 48 位 NCO 可编程抽取率 差分时钟输入 SPI 控制 整数时钟除以 2 和除以 4 灵活的 JESD204B 通道配置 片上抖动可改善小信号线性度

流水线式忆阻神经网络模数转换器

摘要——随着高速、高精度、低功耗混合信号系统的出现,对精确、快速、节能的模数转换器 (ADC) 和数模转换器 (DAC) 的需求日益增长。不幸的是,随着 CMOS 技术的缩小,现代 ADC 在速度、功率和精度之间进行权衡。最近,已经提出了四位 ADC/DAC 的忆阻神经形态架构。可以使用机器学习算法实时训练此类转换器,以突破速度-功率-精度权衡,同时优化不同应用的转换性能。然而,将此类架构扩展到四位以上具有挑战性。本文提出了一种基于四位转换器流水线的可扩展模块化神经网络 ADC 架构,保留了其在应用重新配置、失配自校准、噪声容忍和功率优化方面的固有优势,同时以延迟为代价接近更高的分辨率和吞吐量。 SPICE 评估表明,8 位流水线 ADC 可实现 0.18 LSB INL、0.20 LSB DNL、7.6 ENOB 和 0.97 fJ/conv FOM。这项工作朝着实现大规模神经形态数据转换器迈出了重要一步。

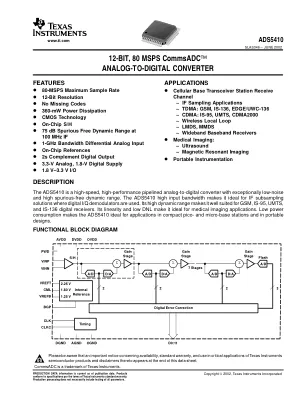

12 位、80 MSPS CommsADC? 模数转换器数据表

ADS5410 是一款 12 位 ADC。其低功耗(360 mW)和 80 Msps 的高采样率是通过使用基于先进低压 CMOS 工艺构建的先进开关电容流水线架构实现的。ADS5410 模拟核心主要采用 3.3 V 电源供电,消耗大部分电量。数字核心采用 1.8 V 电源供电。如果设计中没有 1.8 V 电源,则可以使用 TPS76318 从 3.3 V AVDD 电源获取 1.8 V。为了增加接口灵活性,数字输出电源 (OV DD ) 可以设置为 1.6 V 至 3.6 V。ADC 核心由 10 个流水线级和一个闪存 ADC 组成。每个级产生 1.5 位。上升时钟沿和下降时钟沿都用于每半个时钟将样本通过流水线传输一次,总共六个时钟周期。

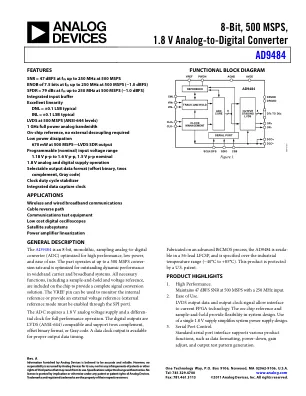

AD9484 | 8 位、500 MSPS、1.8 V 模数转换器

SNR = 47 dBFS,f IN 高达 250 MHz,500 MSPS ENOB 为 7.5 位,f IN 高达 250 MHz,500 MSPS(−1.0 dBFS) SFDR = 79 dBc,f IN 高达 250 MHz,500 MSPS(−1.0 dBFS) 集成输入缓冲器 出色的线性度 DNL = ±0.1 LSB 典型值 INL = ±0.1 LSB 典型值 LVDS,500 MSPS(ANSI-644 级别) 1 GHz 全功率模拟带宽 片上基准电压源,无需外部去耦 低功耗 670 mW,500 MSPS—LVDS SDR 输出 可编程(标称值)输入电压范围 1.18 V p-p 至 1.6 V p-p,1.5 V p-p 标称值 1.8 V 模拟和数字电源操作 可选输出数据格式(偏移二进制、二进制补码、格雷码) 时钟占空比稳定器 集成数据采集时钟

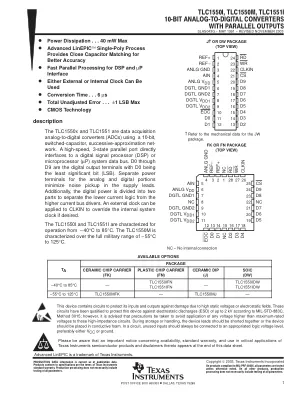

具有并行输出的 10 位模数转换器 数据表 (Rev. G)

电源电压,V DD1 、V DD2 和 V DD3 (见注 1) 6.5 V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .输出电压范围,VO −0.3 V 至 V DD + 0.3 V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 峰值输入电流(任何数字输入) ± 10 mA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .峰值总输入电流(所有输入)± 30 mA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 工作自然通风温度范围,TA:TLC1550I,TLC1551I −40 ° C 至 85 ° C . . . . . . . . . . . . . . . . . . . . TLC1550M −55 ° C 至 125 ° C . . . . . . . . . . . . . . . . . . . 存储温度范围,T stg −65 ° C 至 150 ° C . . . . . . . . . . . . . . . . . . . . . 10 秒外壳温度:FK 或 FN 封装 260 ° C . . . . . . . . . . . . . . . ..................................................................................................................................... 距外壳 1.6 毫米(1/16 英寸)处的引线温度持续 10 秒:J 或 NW 封装 260 °C ....................................................................................................................................

具有并行输出的 10 位模数转换器 数据表 (Rev. G)

电源电压,V DD1 、V DD2 和 V DD3 (见注 1) 6.5 V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .输出电压范围,VO −0.3 V 至 V DD + 0.3 V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 峰值输入电流(任何数字输入) ± 10 mA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .峰值总输入电流(所有输入)± 30 mA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 工作自然通风温度范围,TA:TLC1550I,TLC1551I −40 ° C 至 85 ° C . . . . . . . . . . . . . . . . . . . . TLC1550M −55 ° C 至 125 ° C . . . . . . . . . . . . . . . . . . . 存储温度范围,T stg −65 ° C 至 150 ° C . . . . . . . . . . . . . . . . . . . . . 10 秒外壳温度:FK 或 FN 封装 260 ° C . . . . . . . . . . . . . . . ..................................................................................................................................... 距外壳 1.6 毫米(1/16 英寸)处的引线温度持续 10 秒:J 或 NW 封装 260 °C ....................................................................................................................................

ADS8355 双路、16 位、1 MSPS、同步采样模数转换器数据表 (Rev. A)

(1) 超出绝对最大额定值所列的应力可能会对器件造成永久性损坏。这些只是应力额定值,并不意味着器件在这些或任何超出建议工作条件所列条件的条件下能够正常工作。长时间暴露在绝对最大额定条件下可能会影响器件的可靠性。