XiaoMi-AI文件搜索系统

World File Search System19 单栅极 MOSFET 性能增强,

本研究通过采用高介电常数电介质材料来提高19nm单栅极MOSFET的性能。通过采用高K电介质材料代替SiO2,可以满足MOSFET器件尺寸缩小趋势的要求。因此,实现了具有不同高K电介质材料的19nm n沟道MOSFET器件,并分析了其性能改进。通过Silvaco TCAD工具中的ATHENA模块进行虚拟制造。同时,使用ATLAS模块利用器件特性。还对上述材料进行了模拟,并与相同结构的传统栅极氧化物SiO2进行了比较。最后,结果证明,氧化钛(TiO2)器件是金属栅极钨硅化物(WSix)组合的最佳介电材料。该器件 (WSix/TiO2) 的驱动电流 (ION) 在阈值电压 (VTH) 为 0.534 V 时为 587.6 µA/um,而预测的目标值为 0.530 V,并且 IOFF 相对较低,为 1.92 pA/µm。该 ION 值符合国际半导体技术路线图 (ITRS) 2013 年对低性能 (LP) 技术预测的最低要求。

Si、Si3N4 和 InGaAsP 光学超表面的制造...

MA Gorlach. et al. Nat. Commun., (2018)干法蚀刻是电介质超表面的必要部分!

T 型栅极增强型 AlGaN/GaN MIS-HEMT 中寄生电容的不稳定性

AlGaN/GaN高电子迁移率晶体管(HEMT)或金属绝缘体半导体HEMT(MIS-HEMT),凭借优越的极化诱导高迁移率二维电子气(2DEG),因其高开关速度、低寄生参数和低导通电阻而受到广泛关注,并在高频射频和功率开关应用方面都取得了公认的成功[1-4]。通常在厚钝化电介质(如SiNx)上设置栅极和/或源极场板,以减轻栅极漏极区域的高电场并获得更高的击穿电压[5-7]。它们也有助于抑制表面态引入的电流崩塌[5,8]。然而,场板结构将引入额外的寄生电容,导致更高的VDS×IDS功率损耗和更长的开关持续时间。此外,钝化层还会引入钝化电介质/(Al)GaN界面态,甚至电介质本身的体态,它们的捕获/去捕获过程会引起寄生电容的动态漂移,导致实际应用中开关转换紊乱,dV/dt控制失效[9-11]。

工业先进技术 – 产品观察

金属和无机材料也用于柔性电子产品。金属具有高导电性,可用作电子产品中的导体。其中,银、铜、镍和碳(例如石墨烯)已以各种形式(包括薄片、纳米线、纳米管)用于柔性电子产品。这些金属可以作为金属油墨印刷。无机材料没有或只有有限的导电性,可用作电子产品中的绝缘体(电介质)或半导体。例如,聚合物、氧化钛和氧化锌已用作柔性和印刷电子产品中的半导体。其他几种氧化物和聚合物已被用作电介质,例如 PMMA 和聚氨酯。与粘合剂、溶剂和添加剂结合,这些材料可以印刷在柔性基板上。5

采用磁控溅射层间电介质直接形成 n+ 工艺,用于自对准共面氧化铟镓锌薄膜晶体管

具有交错结构(例如蚀刻停止 (ES) 和背沟道蚀刻 (BCE) 结构)的铟镓锌氧化物 (IGZO) 薄膜晶体管 (TFT) 已被证明可用作平板显示器中的电路器件 [1,2]。然而,由于栅极和源/漏极 (S/D) 电极之间的重叠,这些交错结构器件不可避免地具有较大的寄生电容,从而导致 TFT 器件的工作速度较低。自对准 (SA) 共面结构是克服该寄生电容问题的一种有前途的解决方案 [3]。形成导电的 n + -IGZO 以获得有源 S/D 区和 S/D 电极之间的欧姆接触是 SA 共面器件的重要工艺。已经提出了许多用于该工艺的方法,并且制备的 IGZO 器件具有良好的性能。通常使用等离子体处理(Ar、H2 等)[4,5] 和深紫外(DUV)照射 [6] 。然而,这些解决方案需要一个额外的步骤,如图 1a 所示,这会导致额外的工艺成本。在 SiO2 栅极绝缘体(GI)过蚀刻期间形成 n + -IGZO 是一种简单的方法 [7,8]。然而,当 GI 蚀刻等离子体可以蚀刻 IGZO 薄膜时,这种方法并不适用。最近,已经证明通过简单地涂覆有机层间电介质(ILD)可以形成 n + -IGZO 区域,并且获得了 24 Ω·cm 的沟道宽度归一化 S/D 串联电阻(R SD W)[9]。本报告展示了在 ILD 沉积过程中形成 n + -IGZO 区域的可能性。基于这个想法,其他制造低 R SD W SA 共面 IGZO TFT 的新方法值得研究。在这项工作中,我们使用磁控溅射工艺沉积 SiO x ILD 并同时为 SA 共面 IGZO TFT 形成 n + -IGZO 区域。这样,ILD 沉积和 n + 形成可以合并为一个步骤,如图 1b 所示。制造的器件具有相当低的 R SD W 。降低 IGZO 薄膜的机制

NIST 测量保证1 kHz 电容标准的程序

用于校准 NIST 的三端电容器。NIST 使用的标准电容器是两个参考标准(100 pF 熔融石英电介质商用电容器)和两个检查

通过van der waals Integration

二维(2D)半导体在高性能电子中的实际应用需要与大规模和高质量的电介质进行整合 - 然而,由于它们的悬空无键,这是迄今为止的挑战。在这里,我们报告了一种干介电整合策略,该策略使晶圆尺度和高κ电介质在2D半导体之上转移。通过使用超薄缓冲层,可以预处理下沉积,然后在MOS 2单层的顶部进行机械干燥转移。转移的超薄电介质纤维可以保留晶圆尺度的晶格和均匀性,而无需任何裂缝,表明高达2.8μf/cm 2的电容,等效的氧化物厚度降至1.2 nm,泄漏率降至1.2 nm,泄漏的电源量〜10-7 A/cm 2。Fab的顶栅MOS 2晶体管显示出固有的特性,而没有掺杂效应,启示率为〜10 7,子阈值向下旋转至68 mV/ dec,最低的界面状态为7.6×10 9 cm-2 ev-1。我们还表明,可扩展的顶门阵列可用于构建功能逻辑门。我们的研究为使用具有良好控制厚度,均匀性和可扩展性的行业兼容的ALD工艺提供了可行的途径。

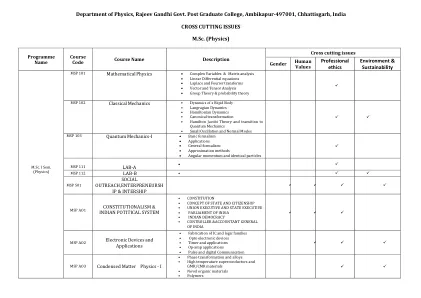

物理系,拉吉夫·甘地政府。研究生学院,Ambikapur-497001,印度恰蒂斯加尔邦 div>

(2)一个带电的圆柱导体,(3)无限的电荷片和两个平行的充电板,电容器,静电场能,电场中导体表面的每单位部位的力,在电场中指导球,以均匀的电场。介电常数,极性和非极性电介质,电介质和高斯定律,介电极化,电动极化矢量P,电位移矢量D.三个电载体,介电敏感性和介电常数和介电常数,二线易感性和极化机制,lorentz local fielt,lorentz lorentz locection和claius fieltriric等方程电介质,稳定电流,电流密度J,非稳态电流和连续性方程,LR,CR和LCR电路中电流的上升和衰减,衰减常数,交流电路,复数及其在解决交流电路问题中的应用,复杂的启发和反应性,串联和平行共振,Q因子,Q因子,Q因子,Q因素,Q因子,AC Coutfer a Ac Coutive a Ac Coutival a ac Coutive aC Ac Coutival aC AC Cower a ac Coution,AC Coution,AC Cower town aC,电动因子,电动因子,发电机,发电机,发电机,发电机,电动因子。