XiaoMi-AI文件搜索系统

World File Search System集成电路的开源设计

摘要 本文介绍了使用 SKY130 开源 PDK 设计自时钟 12 位非二进制全差分 SAR-ADC。整个混合信号电路设计和布局均采用免费开源软件创建。ADC 在 1.8V 电源下达到高达 1.44MS/s 的采样率,同时在 0.175mm 2 的小面积上消耗 703 μW 的功率。可配置抽取滤波器可以在使用 256 的过采样因子时将 ADC 分辨率提高到 16 位。使用 448aF 华夫饼电容器的 9 位温度计编码和 3 位二进制编码 DAC 矩阵导致每个输入的总电容为 1.83pF。使用 SKY130 高密度标准单元的形式来实现可配置的模拟功能,允许使用硬件描述语言对模拟电路进行参数化,并在有意数字化的工作流程中强化宏。

遥控编码集成电路(HS2262)

概述 HS2262 是采用 CMOS 工艺的通用低功耗编码电路。除省电模式外,各电路均包含可更改的地址码和数据码,可用于无线电和红外遥控发射。HS2262 与 PT2262 兼容。 特点: · CMOS 工艺,低功耗 · 最大 6 位数据 · 外设少 · 可达 531,441 个地址码 · 单脚电阻振荡电路 · 红外和无线电遥控应用 · 宽工作电压范围:1.3V~12V · 多种封装选择 应用 · 汽车防盗系统 · 遥控玩具 · 家居防盗系统 · 其他工业遥控器 PAD 分配

集成电路产业处在十字路口

集成电路 (IC) 行业是数字化进程的基础,是当前和未来应用最重要的使能技术。这得益于摩尔定律预测的 IC 工艺的巨大微型化和性能改进,从 1970 年第一款英特尔 4004 微处理器上的约 103 个晶体管开始,到 2022 年 3 月(Apple M1 Ultra)达到 1011 个晶体管 [1],这是前所未有、无与伦比的改进速度,它推动了互联网、移动通信以及现在的智能汽车等发明的诞生。简而言之,每个引入 IC(微芯片或简称芯片)的行业都受益于更高的效率、智能化和扩展的功能。由于这一成功,芯片如今已成为全球第四大交易产品(2021 年出货了 115 万个半导体单元),仅次于原油、机动车及其零部件和成品油。2021 年,芯片市场价值为 0.6 万亿美元,销售额同比增长 26%,预计到 2035 年将达到 1 万亿美元 [2]。一些分析人士甚至将芯片称为新石油,因为芯片为应用提供“动力”,使能够利用尖端技术生产出最高性能芯片的国家在计算和通信能力方面以及从纯粹的军事角度来看都比其他国家更强大。到目前为止,俄乌战争强调的一个概念是,乌克兰军队使用了小型且相对便宜的武器,例如标枪和毒刺防空导弹,它们采用先进的半导体作为制导系统。一颗“标枪”导弹约有 250 块芯片 [3]。西方国家禁止向俄罗斯出口半导体,而俄罗斯自己没有先进的芯片生产能力;没有进口,俄罗斯军方就无法为自己提供精确制导弹药。令人惊讶的是,芯片在全球经济中的关键作用直到最近才得到各国政府的认可和公众辩论。近几十年来,全球经济更多地关注软件和第三产业,而芯片则成为纯粹的商品。然而,新冠疫情和乌克兰战争凸显了芯片短缺(芯片产量不足以满足需求)的问题、全球供应链的脆弱性以及芯片价格的波动性。

集成电路质量和可靠性

Schroder 6. 磁泡记忆技术,Hsu Chang 7. 变压器和电感器设计手册,Colonel Wm. T. McLyman 8. 电磁学:古典和现代理论与应用,Samuel Seely 和 Alexander D. Poularikas 9. 一维数字信号处理,Chi-Tsang Chen 10. 互联动力系统,Raymond A. DeCarlo 和 Richard Saeks 11. 现代数字控制系统,Raymond G. Jacquot 12. 混合电路设计和制造,Roydn D. Jones 13. 变压器和电感器的磁芯选择:实践和规范用户指南,Colonel Wm. T. McLyman 14. 静态和旋转电磁设备,Richard H. Engelmann 15. 节能电动机:选择和应用,John C. Andreas 16. 电磁兼容,Heinz M. Schlicke 17. 电子学:模型、分析和系统,James G. Gottling 18. 数字滤波器设计手册,Fred J. Taylor 19. 多变量控制:简介,PK Sinha 20. 柔性电路:设计和应用,Steve Gurley,Carl A. Edstrom, Jr.、Ray D. Greenway 和 William P. Kelly 供稿 21. 电路中断:理论和技术,Thomas E. Browne, Jr. 22. 开关模式功率转换:基本理论和设计,K. Kit Sum 23. 模式识别:应用于大型数据集问题,单变量

电源管理集成电路

关于导师:Qadeer Khan 教授是印度理工学院马德拉斯分校电气工程系集成电路与系统组的助理教授。他于 1999 年获得印度新德里贾米亚米利亚伊斯兰大学电子与通信工程学士学位,并于 2012 年获得美国俄勒冈州立大学电气与计算机工程博士学位。他的博士工作重点是开发高性能开关直流-直流转换器的新型控制技术。2012 年至 2015 年,他担任高通公司圣地亚哥分公司的电源管理系统主管工程师,2015 年至 2016 年在班加罗尔高通公司工作,参与定义骁龙芯片组各种电源管理模块的系统和架构,以满足不同的智能手机市场需求。 1999 年至 2005 年,他曾就职于摩托罗拉和印度飞思卡尔半导体公司,主要负责设计用于基带和网络处理器的混合信号电路以及用于高压电机驱动器的全芯片集成解决方案。Qadeer Khan 博士拥有 18 项美国专利,并在模拟、混合信号和电源管理 IC 领域撰写/合作撰写了 20 多篇 IEEE 出版物。他担任 IEEE 固态电路杂志、IEEE 超大规模集成系统交易、IEEE 电力电子交易和 IEEE 电力电子快报的审稿人。他的研究兴趣涉及高性能线性稳压器、LDO、开关直流-直流转换器和用于便携式电子产品和能量收集的电源管理 IC

光学集成电路PDF

算法设计:由Michael Goodrich和Roberto Tamassia撰写的算法算法算法设计的全面介绍,提供了有关计算机算法和数据结构的设计,实现和分析的现代视角。本教科书专为本科和初中算法课程而设计,为理论分析技术,设计模式和实验方法提供了全面的介绍。文本包括几个实施案例研究,并利用Internet应用程序来激励诸如哈希,分类和搜索之类的主题。算法设计专注于实用应用,为学生提供了算法技术的坚实基础,这是那些寻求对算法更全面介绍的人的理想资源。 本书提供了对计算机算法和数据结构的全面介绍。 主要目标是向学生介绍算法和数据结构的设计和分析。 本书涵盖了各种主题,例如算法设计模式,例如贪婪,分歧和动态编程;算法框架,包括NP完整性,近似算法和并行算法;以及列表,树和哈希表等数据结构。 组合算法,图形算法,几何算法,数值算法和Internet算法也涵盖在本书中。 他们还积极从事教育技术研究,特别着重于算法可视化系统和对远程学习的基础设施支持。算法设计专注于实用应用,为学生提供了算法技术的坚实基础,这是那些寻求对算法更全面介绍的人的理想资源。本书提供了对计算机算法和数据结构的全面介绍。主要目标是向学生介绍算法和数据结构的设计和分析。本书涵盖了各种主题,例如算法设计模式,例如贪婪,分歧和动态编程;算法框架,包括NP完整性,近似算法和并行算法;以及列表,树和哈希表等数据结构。组合算法,图形算法,几何算法,数值算法和Internet算法也涵盖在本书中。他们还积极从事教育技术研究,特别着重于算法可视化系统和对远程学习的基础设施支持。作者,古德里奇(Goodrich)和塔玛西亚(Tamassia)教授是数据结构和算法领域的知名研究人员,并发表了许多有关互联网计算,信息可视化,地理信息系统和计算机安全等主题的论文。作者拥有广泛的研究合作记录,并在国家科学基金会,陆军研究办公室和国防高级研究计划局赞助的几个联合项目中担任首席研究人员。Roberto Tamassia获得了博士学位。 1988年,伊利诺伊大学伊利诺伊大学的电气和计算机工程专业。他目前是计算机科学系教授,也是布朗大学几何计算中心主任。他是计算几何形状的编辑:理论和应用以及图形算法和应用杂志,并以前曾在计算机IEEE交易的编辑委员会任职。除了他的研究成就外,塔马西亚在教学方面还具有丰富的经验。自1987年以来,他一直在教授数据结构和算法课程,其中包括新生 - 学生级课程和高级课程,以这种能力获得了几项教学奖项。塔马西亚的教学风格涉及活泼的互动课堂会议,这些课程带来了数据结构和算法技术背后的直觉和见解。Tamas-Sia博士已将数据结构和算法教授为自1988年以来的入门新生课程。学生会发现主题有趣且与互联网应用程序相关。使他的教学风格与众不同的一件事是他有效地利用了互动超文本演讲,延续了布朗的“电子课堂”传统。他所教的课程精心设计的网页已被全球学生和专业人士用作参考材料。算法和与网络相关的主题,例如缓存路由,拍卖机制和爬行技术。我们发现,通过现实世界的应用介绍这些主题并激励学生学习算法可以提高他们的理解。本书提供了Java中的软件实施示例,面向实验分析的实现问题以及各种设计方法。讲师可以根据其喜好构建材料的灵活性,涵盖或跳过某些章节,因为他们认为合适。这本书是围绕算法课程进行的,具有传统算法介绍(CS7)课程或专门的Internet算法课程的可选选择。表0.1提供了一个示例,说明了如何将此材料用于每章,而表0.2提供了另一种选择。此外,该书还提供了一个全面的网站,其中包括大量资源,示例和实施问题与算法和与Internet相关的主题相关的问题。为了增强学习经验,我们提供了补充本书中主题的其他教育辅助工具。我们假设读者对基本数据结构(例如数组和链接列表)有基本的了解,并且熟悉C,C ++或Java(例如C,C ++或Java)等高级编程语言。对于学生,这些资源包括: *以四页格式的大多数主题的演示讲义 *一个有关选定作业的提示的数据库,由问题编号索引 *互动式的小程序,这些互动式小程序可以为本书的Java示例提供基本数据结构和算法 *源代码,而这本书中的Java示例特别有用,这对您的提示服务特别有用,这可能会对某些学生挑战一些学生。For instructors using this book, we offer a dedicated section of the website with additional teaching aids such as: * Solutions to selected exercises in this book * A database of additional exercises and their solutions * Presentations (one-per-page format) for most topics covered in this book Readers interested in implementing algorithms and data structures can download JDSL, the Data Structures Library in Java, from .算法在高级“伪代码”中描述,而特定的编程语言构造仅在可选的Java实现示例部分中使用。在数学背景方面,我们假设读者熟悉一年级数学的主题,包括指数,对数,求和,限制和基本概率。我们在第1章中回顾了大多数这些主题,包括指数,对数和总结,并在附录A中提供了其他有用的数学事实(包括基本概率)的总结。 Algorithm 373-376 8 Network Flow and Matching 381-412 8.1 Flows and Cuts 8.2 Maximum Flow 8.3 Maximum Bipartite Matching 8.4 Minimum-Cost Flow: 8.5 Java Example: Minimum-Cost Flow 398-412 8.6 Exercises **Part II: Internet Algorithmics** 9 Text Processing 417-444 9.1 Strings and Pattern Matching Algorithms 9.2 Tries 9.3 Text Compression 9.4 Text Similarity Testing 9.5 Exercises 10 Number Theory and Cryptography 451-508 10.1 Fundamental Algorithms Involving Numbers 10.2 Cryptographic Computations 10.3 Information Security Algorithms and Protocols 10.4 The Fast Fourier Transform 10.5 Java Example: FFT 500-508 10.6 Exercises **Target Audience** * Computer Programmers * Software Engineers * Scientists **Special Features** * Addresses数据结构和算法的实现 *涵盖了密码,FFT,并行算法和NP完整性

开发下一代光子集成电路

开发下一代光子集成电路 在过去二十年里,硅光子学 1,2 已经从学术研究转向广泛的工业应用。然而,尽管硅光子学 3 取得了商业上的成功,被用于数据中心的收发器,但硅并不是光子学和光学的理想材料。硅的带隙为 1 eV,因此不能用于可见光的生成和处理 4,5 ;另外,硅不能承受高光功率。同样,即使在最先进的全球代工厂的硅光子商业生产线中,使用数十亿美元的制造设备,损耗水平也只有每厘米 1dB。事实上,在芯片中获得超低损耗是极具挑战性的。对如此低损耗的追求不仅仅是一项学术努力:从历史上看,高锟的工作还为损耗仅为 1dB/km 的光纤奠定了基础,这导致了 2008 年诺贝尔物理学奖并彻底改变了通信领域 6 。然而,直到最近,低损耗集成光子电路的进展几十年来一直停滞不前——在 dB/cm 的水平。然而,芯片上的超低传播损耗对于众多未来应用至关重要。

在集成电路上塞入更多元件

集成电子学的未来就是电子学本身的未来。集成的优势将带来电子学的普及,推动这门科学进入许多新领域。集成电路将带来许多奇迹,如家用计算机(或至少是与中央计算机相连的终端)、汽车自动控制装置和个人便携式通信设备。如今,电子手表只需要一个显示器就可以实现。但最大的潜力在于生产大型系统。在电话通信中,数字滤波器中的集成电路将分离多路复用设备上的信道。集成电路还将切换电话电路并执行数据处理。计算机将更加强大,并将以完全不同的方式组织。例如,由集成电子学构建的存储器可能分布在整个

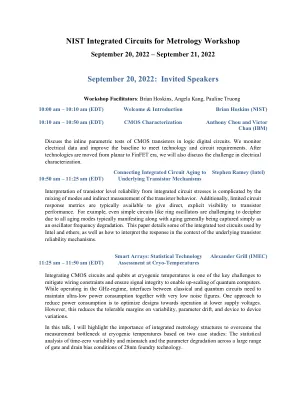

NIST 计量集成电路研讨会

21 世纪海量数据工作负载(例如 AI/机器学习)的计算需求远远超出了当今计算系统的能力。随着问题规模的扩大,这一挑战变得更加严峻,尤其是随着传统晶体管小型化变得越来越困难。本次演讲将介绍变革性的纳米系统,旨在实现 1,000 倍系统级能量延迟产品优势,尤其是针对海量数据工作负载。我们通过超密集(例如单片)3D 逻辑和内存集成(N3XT 3D 方法)创建新的芯片架构。通过芯片堆叠/中介层/晶圆级集成的连续性集成多个 N3XT 3D 芯片(N3XT 3D MOSAIC)。在工业和研究制造设施中建造的几个硬件原型证明了我们方法的有效性。尽管设计缺陷、制造缺陷、可靠性故障和安全攻击等挑战日益严峻,我们还提出了确保系统稳健运行的新方法。例如,当今的测试和诊断方法无法满足当今(和未来)系统(从(自动驾驶)汽车到云端)所要求的全面性水平。我们还将讨论解决这些稳健性挑战的新“系统驱动”方法。