机构名称:

¥ 1.0

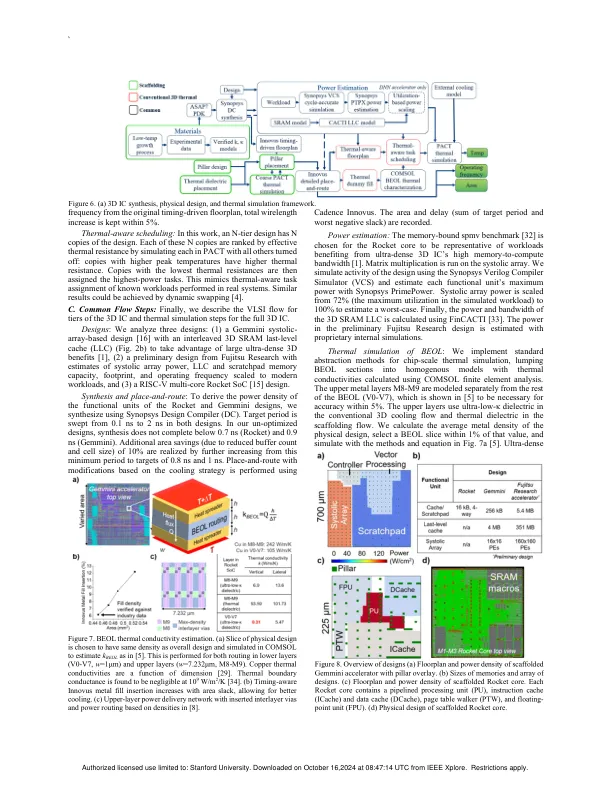

与传统的 2D 计算系统相比,超密集 3D 集成电路(3D IC),例如单片 3D IC(图 1),可以为数据密集型应用带来巨大的能量延迟积(EDP)优势 [1,2]。为了实现这些优势,需要将多层逻辑和存储器(例如,逻辑和/或存储器设备的薄层,以及相关的信号/全局金属布线)以 3D 形式集成,并使用有限长宽比的后端制程(BEOL)层间过孔(ILV)建立超密集(例如,间距 ≤ 100 纳米)垂直连接 [3]。现有的 BEOL 布线结构已经在使用这种纳米级 ILV。3D IC 变得至关重要,因为工艺技术小型化的根本限制使得传统的缩放路径更加困难。但是,必须克服重大的热挑战才能在多个 3D 层上实现高速和高功率计算引擎 [4-5]。如果没有新技术,未来 3D IC 的上层最高温度将大大超过可靠运行所需的上限(例如 [6] 中的 125°C)。我们使用图 1 中的单片 3D IC 来了解 3D 层中的温升和热耗散(详细分析见第 III 部分)。图 1 中的 N 层中的每一层都包含一层高速、高功率硅逻辑器件(例如,计算引擎)和由铜布线和超低κ 层间电介质 (ILD) 组成的 BEOL 层(例如,用于信号布线)。各层通过超密集 ILV 电连接。在某些设计中,每层还存在硅存储器、存储器访问设备和额外的 BEOL。3D IC 由附加的散热器进行外部冷却,散热器将产生的所有热量以散热器比传热系数 h(W/m 2 /K)散发到环境中。最高温度 T j 取决于散热器、环境温度和 N 层的热特性。散热器创新(如 [7])只需散热器上 10°C 的温升(即 h= 10 6 W/m 2 /K)即可消除 1000 W/cm 2 的热量,尽管

超高密度 3D 集成电路的热支架

主要关键词