XiaoMi-AI文件搜索系统

World File Search SystemPython 中的集成电路布局图像渲染工具

您可能会注意到,黄绿色、红色、金色和粉红色以 RGB 颜色代码表示。GDS 层编号和名称可在 PDK 图层图文件中找到(参见图 1(a)),而颜色及其代码可在技术文件中获得(参见图 1(b))。通常有一个用户友好的图层窗口 (LSW) 可帮助在请求的 LayerColors.map 中转换两个文件。可以实现一个自动化工具来进行此类转换。但是,此过程每个 PDK 仅运行一次。不同 PDK 版本之间的 GDS 编号、层名称和颜色不会改变。此外,CAD 工具通常使用示例中提出的颜色代码。因此,仅在安装新的 PDK 时才需要此过程。GDS 编号是不同 PDK 文件之间变化最大的数据。商业 PDK 中的图层颜色通常相似,例如(XFAB Mixed-Signal Foundry Experts,2019 年)。

氮化硅光子集成电路原型制作及小批量生产

免责声明 - 本信息按“原样”提供,不作任何陈述或保证。Imec 是 IMEC International(根据比利时法律成立的法人实体,名称为“stichting van openbaar nut”)、imec Belgium(由弗兰德政府支持的 IMEC vzw)、imec the Dutch(Stichting IMEC Nederland,由荷兰政府支持的 Holst Centre 的一部分)、imec Taiwan(IMEC Taiwan Co.)、imec China(IMEC Microelectronics (Shanghai) Co. Ltd.)、imec India(Imec India Private Limited)、imec Florida(IMEC USA 纳米电子设计中心)活动的注册商标。

2024 IEEE自定义集成电路会议(CICC)21

3:50 pm 11-6:70-通道频率频率的每通道冷冻-CMOS IC的7.4μW和860μm²,半导体Qubits的μs读取“ Quentin Schmidt先生(法国)1,Brian Martinez(France)1,Thomas Houriez(France)(France)1,France)1,Brian Martinez先生(France)。 (法国)1,Aloysius Jansen博士(法国)2,Xavier Jehl博士(法国)2,Tristan Meunier博士(法国)3,GaëlPillonnet博士(法国)1,GérardBilliot(法国)1,法国先生(法国)1,Adrien Morel(法国)4,France(France)(France)(France)5,France)5,5,France)5,5,5,France),5,5大学。Grenoble Alpes,CEA,Leti,F-38000 Grenoble,法国,2。大学。Grenoble Alpes,CEA,Pheliqs,F-38000 Grenoble,法国,3。Quobly,F-38000 Grenoble,法国;大学。Grenoble Alpes,CNRS,Institut Neel,F-38000 Grenoble,法国,4。Symme,Univ。Savoie Mont Blanc,法国Annecy,5。大学。Grenoble Alpes,CEA,List,F-38000 Grenoble,法国)

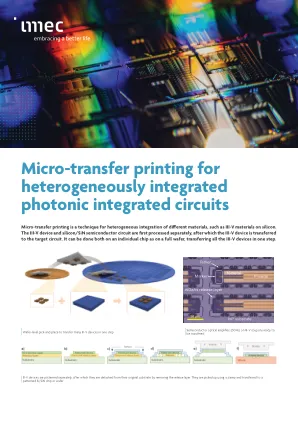

异质集成光子集成电路的微转移打印

免责声明 - 本信息按“原样”提供,不作任何陈述或保证。Imec 是 imec International(IMEC International,根据比利时法律成立的法人实体,名称为“stichting van openbaar nut”)、imec Belgium(由弗兰德政府支持的 IMEC vzw)、imec the Dutch(Stichting IMEC Nederland)、imec China(IMEC Microelectronics (Shanghai) Co. Ltd.)、imec India(IMEC India Private Limited)、imec San Francisco(IMEC Inc.)和 imec Florida(IMEC USA Nanoelectronics Design Center Inc.)活动的注册商标。

集成电路专用逻辑加密的全球性攻击及补救措施

摘要 —近年来,半导体行业将制造外包给低成本但不一定值得信赖的代工厂。这种无晶圆厂商业模式面临着新的安全挑战,包括盗版和生产过剩。一种防止未经授权产品运行的经过充分研究的解决方案是逻辑加密,其中使用只有设计人员知道的密钥对芯片进行加密。然而,大多数逻辑加密解决方案都容易受到密钥一致性和探测攻击。在本文中,我们首先提出 GSAT,一种对使用 SAT 模型的现有 IC 特定逻辑加密方案的全局攻击,它可以有效解密可插入所有加密 IC 的隐藏全局密钥。接下来,我们提出了一种高度安全且低成本的补救措施,称为 SPLEnD:基于强 PUF 的逻辑加密设计。传统的 IC 特定加密方案容易受到 GSAT 攻击,而 SPLEnD 不仅可以有效抵抗 GSAT,而且还平衡了安全性和效率。

电子集成电路和系统中 SET 效应的表征

软错误: 中子单粒子翻转 (NSEU) 单粒子瞬变 (SET) 单粒子翻转 (SEU) 单粒子功能中断 (SEFI)

面向下一代太空应用的光子集成电路 (PIC)

即插即用:硅光子模块将电子数据转换为光子,然后再转换回来。硅电路帮助光调制器将电子数据编码为几种颜色的光脉冲。光通过光纤传输到另一个模块,光电探测器将光重新转换为电子比特。电子数据再次由硅电路处理并发送到适当的服务器。

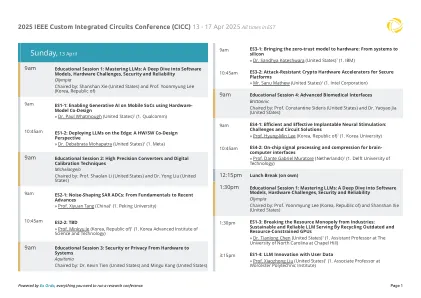

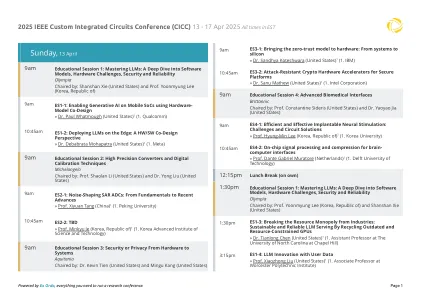

2025 IEEE自定义集成电路会议(CICC)13

1:30 pm 10-1 :(被邀请)类似基于变压器的语言模型(被邀请)类似类似的硬件加速器»Geoffrey W. Burr(美国)1,Hsinyu Tsai(美国)1,IEM Boybat(瑞士)博士(瑞士)2,William A. Simon(Switzerland) Vasilopoulos(瑞士)2,Pritish Narayanan博士(美国)1,Andrea Fasoli博士(美国)1,Kohji Hosokawa先生(日本)3(日本)3,Manuel Lealoo(瑞士)博士(瑞士)2国家)1,查尔斯·麦金(Charles Mackin)(美国)1,埃琳娜·费罗(Elena Ferro)(瑞士)2,Kaoutar El Maghraoui博士(美国)4,Hadjer Benmeziane博士(瑞士)2,Timothy Philicelli(美国)5,美国的Timothy Philicelli博士(瑞士) ,Shubham Jain博士(美国)4,Abu Sebastian博士(瑞士)2,Vijay Narayanan博士(美国)4(1。IBM研究-Almaden,2。IBM Research Europe,3。IBM东京研究实验室,4。 IBM T. J. Watson Research Center,5。 IBM Albany Nanotech)IBM东京研究实验室,4。IBM T. J. Watson Research Center,5。 IBM Albany Nanotech)IBM T. J. Watson Research Center,5。IBM Albany Nanotech)IBM Albany Nanotech)

2025 IEEE自定义集成电路会议(CICC)13

1:30 pm 10-1 :(被邀请)类似基于变压器的语言模型(被邀请)类似类似的硬件加速器»Geoffrey W. Burr(美国)1,Hsinyu Tsai(美国)1,IEM Boybat(瑞士)博士(瑞士)2,William A. Simon(Switzerland) Vasilopoulos(瑞士)2,Pritish Narayanan博士(美国)1,Andrea Fasoli博士(美国)1,Kohji Hosokawa先生(日本)3(日本)3,Manuel Lealoo(瑞士)博士(瑞士)2国家)1,查尔斯·麦金(Charles Mackin)(美国)1,埃琳娜·费罗(Elena Ferro)(瑞士)2,Kaoutar El Maghraoui博士(美国)4,Hadjer Benmeziane博士(瑞士)2,Timothy Philicelli(美国)5,美国的Timothy Philicelli博士(瑞士) ,Shubham Jain博士(美国)4,Abu Sebastian博士(瑞士)2,Vijay Narayanan博士(美国)4(1。IBM研究-Almaden,2。IBM Research Europe,3。IBM东京研究实验室,4。 IBM T. J. Watson Research Center,5。 IBM Albany Nanotech)IBM东京研究实验室,4。IBM T. J. Watson Research Center,5。 IBM Albany Nanotech)IBM T. J. Watson Research Center,5。IBM Albany Nanotech)IBM Albany Nanotech)

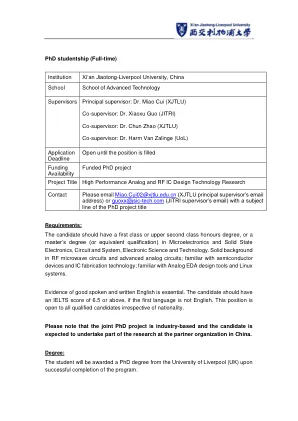

博士学位(全职)机构xi'an jiaotong- ...

这个博士学位项目是苏州(http://www.xjtlu.edu.cn)之间的一个合作研究项目(智能集成电路设计技术)。博士学位的学生可以在三年内获得学生的令人满意的进度。该奖项涵盖了三年的学费(目前相当于每年80,000元人民币)。此外,在苏州学院进行主要研究期间,将由智能综合电路设计技术研究所以每月5000 RMB的标准津贴为每月5000 RMB提供每月的生活津贴。项目描述: