XiaoMi-AI文件搜索系统

World File Search System引入了用于光子集成电路设计的新范式 - 最终

● Head Office: Canada, founded in 2006 ● Branch Offices: CBS Japan (2006) & CBS Europe (2020) ● Additionally: We provide specialized tools for opto-mechanical simulation (FRED) and optical measurement systems (opsira) to support the full optical development cycle ● Today's Presenter: Tom Davies, COO

碳化硅纳米线场效应晶体管在集成电路和传感应用方面的进展

摘要。块体碳化硅 (SiC) 的优越物理特性以及一维 (1D) 纳米结构特定物理特性的预期增强,激发了一系列针对纳米线 (NW) 制造和特性以及其在器件中的应用的研究。SiC 纳米线场效应晶体管 (NWFET) 是研究 SiC NW 在外部刺激(如电场)(集成电路中的应用)或 NW 表面上存在力或化学/生物物种(传感器中的应用)时在不同温度下的电特性的理想器件概念。SiC NW 量子传输建模的初步报告揭示了实现与 Si 基 NWFET 相当性能的前景。然而,实验性的 NWFET 演示表现出较低的载流子迁移率、I ON /I OFF 比和跨导 (gm ) 值,这对其进一步发展构成了障碍。低性能主要源于高度无意掺杂和未优化的 SiO 2 /SiC NW 界面。事实上,由于缺乏对 SiC NW 自下而上的生长过程的严格控制,导致非常高的载流子浓度(主要源于无意掺杂)接近退化极限。高密度陷阱和固定电荷的低界面质量导致栅极电场屏蔽,并表明需要进一步研究 SiO 2 /SiC NW 界面。由于这两种影响,即使在非常高的栅极电压下也无法实现器件关断。目前,只有在源/漏极 (S/D) 区域具有肖特基势垒 (SB) 的背栅极 NWFET 才表现出明确的关断和改进的性能,这要归功于通过全局栅极作用间接调制漏极电流,从而调节 S/D 区域的 SB 透明度。

基于直方图的自动分割:从 SEM 图像中分割集成电路结构的新方法

摘要 — 在逆向工程和硬件保证领域,大多数数据采集是通过电子显微镜技术(如扫描电子显微镜 (SEM))完成的。然而,与光学成像中的同行不同,只有有限数量的技术可用于增强和提取原始 SEM 图像中的信息。在本文中,我们介绍了一种从 SEM 图像中分割出集成电路 (IC) 结构的算法。与本文讨论的现有算法不同,该算法是无监督的、无参数的,并且不需要关于噪声模型或目标图像中特征的先验信息,这使得它在低质量图像采集场景中也有效。此外,还报告并讨论了该算法在 IC 中各种结构和层上的应用结果。索引术语 — 逆向工程、硬件保证、SEM、分割

2023 年 7 月 IEEE TAXONOMY 版本 1.02

........非线性网络分析 ........电路故障 ........电气故障检测 ........电路噪声 ........热噪声 ........电路模拟 ........电路综合 ........高级综合 ........集成电路综合 ........协处理器 ........计数电路 ........耦合电路 ........数字电路 ........电路拓扑 ........数字集成电路 ........数字信号处理器 ........分布参数电路 ........驱动电路 ........电子电路 ........面包板 ........中央处理单元 ........多谐振荡器 ........条板电路 ........等效电路 ........反馈 ........反馈电路 ........负反馈 ........神经反馈 ........混合集成电路 ........集成电路 ........模拟集成电路 ........模拟-数字集成电路 ........专用集成电路 ........CMOS集成电路 ........协处理器 ........电流模式电路............数字集成电路............FET集成电路............现场可编程门阵列............混合集成电路............集成电路互连............集成电路建模............集成电路噪声............集成电路合成............大规模集成............MESFET集成电路

带有商用收发器集成电路的通信组件的空间环境评估和低地球轨道演示

摘要:软件可控的消费级单芯片收发器集成电路 (IC) 具有多种应用,因为它可以生成连续波信标,同时提供频移键控数字通信的基本功能。此外,这种 IC 成本低廉。上述特点对于空间有限的立方体卫星和开发成本受限的大学卫星非常有利。在本研究中,我们进行了辐射耐受性评估和多普勒频移耐受性测试,以评估单芯片消费收发器 IC 在太空应用中的可行性。在辐射耐受性评估测试中,我们将 IC 的辐射耐受性与在太空中实施的单片机的辐射耐受性进行比较,并根据单粒子翻转发生率的预测分析确认前者的良好抗性。通过多普勒频移耐受性测试,我们确认了合适的接收灵敏度。此外,我们开发了一个收发器 IC 作为立方体卫星级卫星组件,并在轨道演示中成功建立通信,其中收发器 IC 用作从国际空间站释放的立方体卫星通信模块。因此,证明了消费通信集成电路的空间利用的可行性,这对于使用新推出的消费设备开发更灵活、更具挑战性的系统设计具有重要意义。

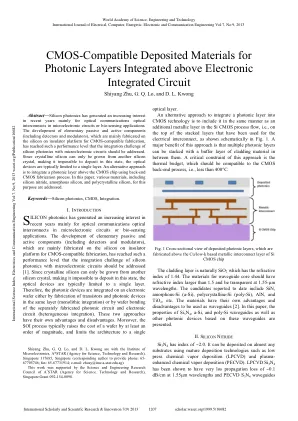

用于集成在电子集成电路上方的光子层的 CMOS 兼容沉积材料

摘要 — 近年来,硅光子学引起了越来越多的关注,主要用于微电子电路或生物传感应用中的光通信光互连。主要在绝缘体上硅平台上制造的用于 CMOS 兼容制造的基本无源和有源元件(包括探测器和调制器)的开发已达到如此高的性能水平,以至于应该解决硅光子学与微电子电路的集成挑战。由于晶体硅只能从另一个硅晶体中生长,因此无法在这种状态下沉积,因此光学器件通常仅限于单层。另一种方法是使用后端 CMOS 制造工艺在 CMOS 芯片上方集成光子层。本文讨论了用于此目的的各种材料,包括氮化硅、非晶硅和多晶硅。关键词 — 硅光子学、CMOS、集成。

表面等离子体共振 (SPR) 光谱和光子集成电路 (PIC) 生物传感器:比较综述

摘要:无标记直接光学生物传感器(如表面等离子体共振 (SPR) 光谱)已成为集中实验室生化分析的黄金标准。基于光子集成电路 (PIC) 的生物传感器基于相同的物理传感机制:衰减场传感。如果能够克服从研究实验室转移到工业应用的挑战,基于 PIC 的生物传感器可以在医疗保健中发挥重要作用,尤其是对于即时诊断。研究正处于这一门槛,这为卫生和环境领域的创新现场分析提供了巨大的机会。通过将创新的 PIC 技术与成熟的 SPR 光谱进行比较,可以更深入地了解它。在本文中,我们简要介绍了这两种技术,并揭示了它们的异同。此外,我们回顾了一些最新进展,并从表面功能化和传感器性能方面比较了这两种技术。

用于 COVID-19 严重程度监测的表面等离子体共振成像 (SPRi) 和光子集成电路 (PIC)

摘要:直接光学检测方法,例如表面等离子体共振成像 (SPRi) 和基于光子集成电路 (PIC) 的生物传感器,可实时快速无标记检测 COVID-19 抗体。每种技术,即 SPRi 和 PIC,在吞吐量、小型化、多路复用、系统集成和具有成本效益的大规模生产方面都有优点和缺点。然而,这两种技术在传感机制方面有相似之处,都可以用作护理点或护理点附近的高含量诊断,其中分析物不仅被量化,而且被全面表征。这很重要,因为最近的结果表明,不仅三种同型 IgM、IgG 和 IgA 的抗体浓度,而且结合强度(亲和力)都可以指示潜在的 COVID-19 严重程度。具有高滴度低亲和力抗体的 COVID-19 患者与疾病严重程度有关。从这个角度来看,我们提供了一些见解,说明如何有效结合 SPR 和 PIC 技术并相互补充,以全面监测 COVID-19 严重程度。这为立即做出治疗决定开辟了一条途径,使患者在感染的早期阶段得到治疗,从而大大降低病情发展为严重阶段的风险。

3D集成电路中Cu⠍Sn⠍Cu微焊盘电迁移失效的实验研究

垂直堆叠的三维集成电路 (3D IC) 中的芯片间电通信由芯片间微凸块实现。微凸块的电迁移可靠性对于了解基于 3D IC 的微电子系统的可靠性至关重要。本文报告了通过热压键合在两个芯片之间形成的 Cu-Sn-Cu 微凸块的电迁移可靠性的实验研究。双芯片 3D IC 组装在线键合陶瓷封装中,并在不同温度下的空气和氮气环境中进行电迁移测试。测量了微连接链和开尔文结构的故障寿命和平均故障时间 (MTTF)。结果表明,Cu-Sn 微连接的本征活化能介于 0.87 eV 和 1.02 eV 之间。基于故障分析,提出了可能的故障机制。这项研究的结果有望提高人们对 3D IC 中电迁移可靠性的根本理解,并促进基于 3D IC 的稳健可靠的微电子系统的开发。2014 Elsevier BV 保留所有权利。

安集科技(688019.SH) 国内CMP抛光液领先企业

在集成电路制造过程中,晶圆表面状态及洁净度是影响晶圆良率和器件质量与可靠性的最重要因素之一,化学机械抛光 ( CMP )、湿法清洗、刻蚀、电化学沉积(电镀)等表面技术扮演重要的作用。公司围绕液体与固体衬底表面的微观处理 技术和高端化学品配方核心技术,专注于芯片制造过程中工艺与材料的最佳解决方案,成功搭建了 “ 化学机械抛光液 - 全品类 产品矩阵 ” 、 “ 功能性湿电子化学品 - 领先技术节点多产品线布局 ” 、 “ 电镀液及其添加剂 - 强化及提升电镀高端产品系列战略供 应 ” 三大核心技术平台。