机构名称:

¥ 2.0

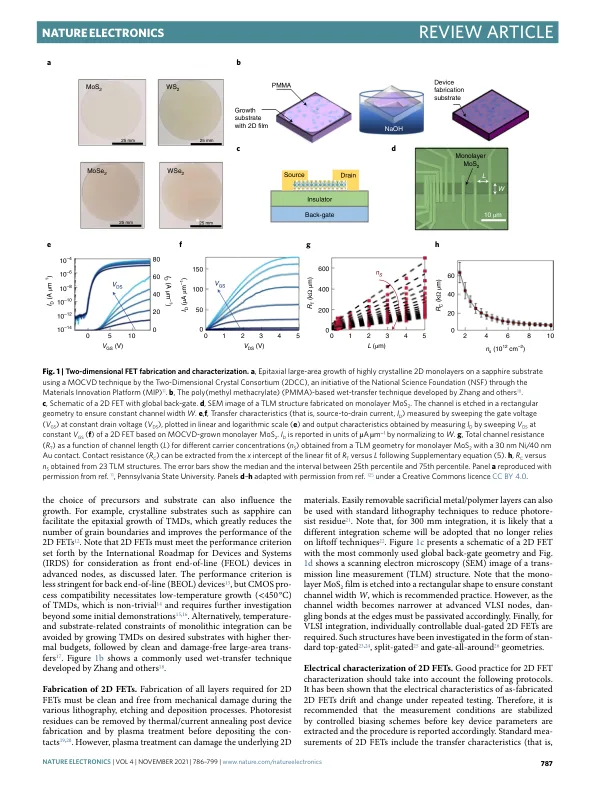

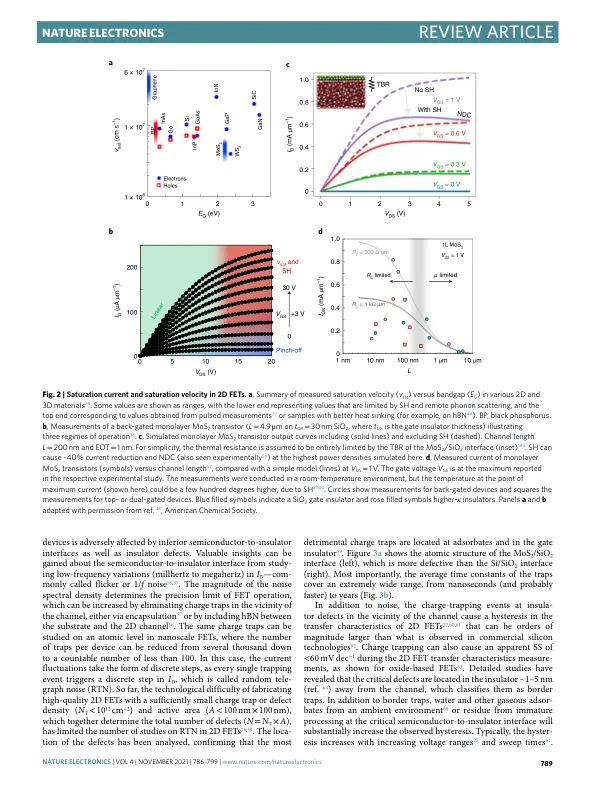

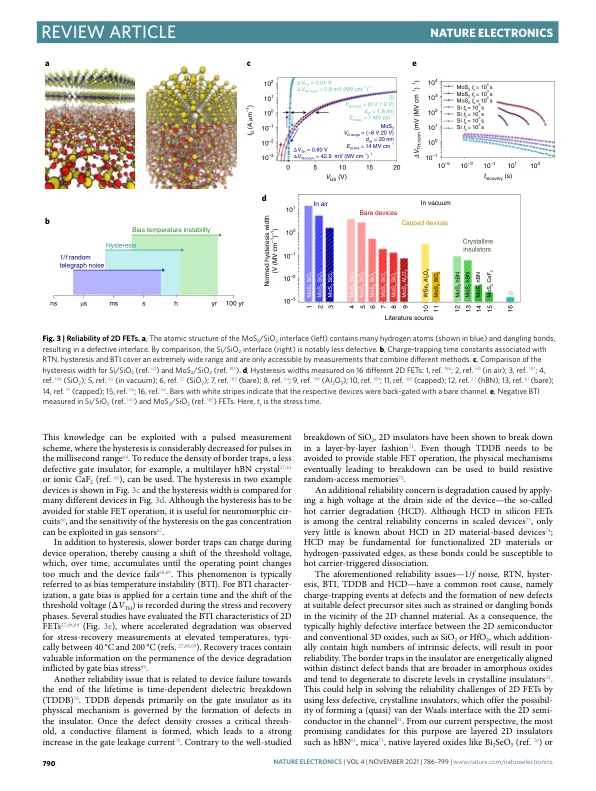

硅互补金属氧化物半导体 (CMOS) 技术的缩放已达到 10 纳米以下技术节点,但进一步缩放越来越具有挑战性,因为器件的栅极静电要求大幅减少沟道厚度以保持所需的性能 1 。场效应晶体管 (FET) 的最终沟道厚度可能在 1 纳米以下范围内。但是,任何三维 (3D) 半导体晶体都无法轻易实现这一点,因为在沟道到电介质界面处电荷载流子的散射增加,导致迁移率严重下降 2 。二维 (2D) 半导体材料单层厚度约为 0.6 纳米,可以提供解决方案。这类材料包括过渡金属二硫属化物 (TMD),其通式为 MX 2 ,其中 M 是过渡金属(例如,Mo 或 W),X 是硫属元素(例如,S、Se 或 Te)3 – 8。材料中没有悬空键也提供了实现更好的通道到电介质界面的潜力。基于机械剥离的单晶 2D 薄片的早期研究,以及基于大面积生长的合成 2D 单层的最新发展,都表明了 2D 晶体管的良好特性。然而,仍有许多挑战有待解决,这使得 2D FET 在未来超大规模集成 (VLSI) 技术中的应用潜力尚不明确。在本篇评论中,我们探讨了 2D FET 在未来集成电路中的发展。我们首先考虑大面积生长

基于二维材料的晶体管,用于未来集成电路

主要关键词