XiaoMi-AI文件搜索系统

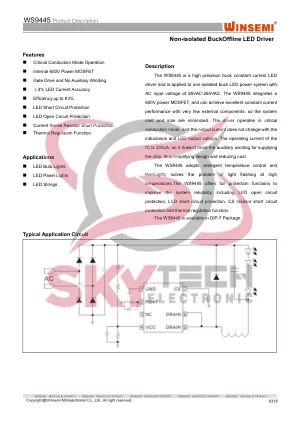

World File Search SystemWS9445-非分离的Buckoffline LED驱动程序

注意:1。我们强烈建议客户在购买我们的产品时仔细检查商标;如果有任何疑问,请不要犹豫与我们联系。2.当电路设计时,请不要超过设备的绝对最大评分。3.WINSEMI Microelectronics Co.,Ltd保留在此规范表中进行更改的权利,并如有更改,恕不另行通知。

综述。量子电路合成与编译...

摘要 量子计算被视为后摩尔时代有望突破计算能力瓶颈的有前途的计算范式。量子处理器尤其是超导量子处理器的日趋成熟为量子算法的开发和实现提供了更多的可能性。作为量子算法实现的关键阶段,逻辑电路设计和量子编译也受到广泛关注,涉及量子逻辑电路综合(又称量子架构搜索)与优化、量子比特映射与路由等关键技术。近期研究表明,相关算法的规模和精度正在稳步提升,尤其是随着人工智能方法的融合。本文系统地回顾和总结了大量文献,探索从算法层面到量子硬件一体化设计优化方案的可行性,将逻辑电路设计和编译优化步骤结合起来,利用人工智能算法卓越的认知和学习能力,可以降低人工设计成本,提高执行精度和效率,促进量子算法在硬件上的实现和验证其优越性。

EEE 433 模拟集成电路

家庭作业问题将来自本文。 3)我将大量使用自己的课堂笔记 讲师 Ahmed Helmy,教员助理,ahmed.helmy@asu.edu 每节课后的办公时间,也可根据需要 Zoom 会议 课程目标:模拟电路、模拟电子器件的设计、分析、模拟和测试,重点是集成电路设计,包括主题:直流偏置、运算放大器。实验室将专注于设计运算放大器。设计、分析和模拟将使用 CADENCE 完成。学生将模拟和布局电路。 课程成果:模拟电路、模拟电子器件的设计、分析、模拟和测试,重点是集成电路设计,包括主题:直流偏置、运算放大器。用于模拟实验室和家庭作业问题的 Cadence。课程主题:1. 简介 2. MOSFET 晶体管 3. 波特图和 dB 4. 集成共源放大器 5. 共源共栅放大器、缓冲器和镜像 6. 差分对放大器 7. 高带宽 CMOS 运算放大器设计 8. CMOS 运算放大器设计示例 9. 反馈放大器 10. 噪声基础知识 11. 模拟 IC 设计规则和布局

减少场耦合纳米技术中的导线交叉

摘要 — 在电路设计领域,与传统的基于晶体管的逻辑相比,场耦合纳米技术 (FCN) 等新兴技术提供了独特的机会。然而,FCN 也带来了一个关键问题:线路交叉对电路稳健性的重大影响。这些交叉要么无法实现,要么会严重降低信号完整性,对高效电路设计造成重大障碍。为了应对这一挑战,我们提出了一种新方法,专注于减少 FCN 电路中的线路交叉。我们的方法引入了 LUT 映射和分解的组合,旨在在逻辑综合过程中产生有利的网络结构,以最大限度地减少线路交叉。这个新的优化指标优先于节点数和关键路径长度,以有效应对这一挑战。通过实证评估,我们证明了所提出方法的有效性,可将线路交叉的第一次近似值降低 41%。69%。这项研究为推进新兴电路技术中的线路交叉优化策略做出了重大贡献,为后 CMOS 逻辑时代更可靠、更高效的设计铺平了道路。

评估NISQ ERA设备中噪声对变异量子电路的影响

摘要 - 量子量的有限供应和明显的量子噪声对嘈杂的中等规模量子(NISQ)时代的量子算法的能力施加了限制。NISQ设备具有多种应用,例如变分量子电路(VQC),它为困难优化和机器学习问题提供了答案。本文对NISQ环境中的量子变量分类进行了详尽的研究,重点是理解噪声对各种特征地图和VQC的影响。我们使用各种数据集评估量子分类器的有效性,从直接的二进制分类问题到更复杂的任务。我们的结果揭示了在减轻噪声效果,识别即使在嘈杂的情况下也表现出鲁棒性的特定量子电路设计中特征图和变异电路选择发挥作用的关键作用。为了强调量子机学习在解决NISQ设置中的复杂问题中的潜力,本研究强调了特征映射选择,变化电路设计,数据集复杂性和量子噪声之间的微妙相互作用。索引项 - 各个量子电路,NISQ设备,噪声,特征图,量子分类器。

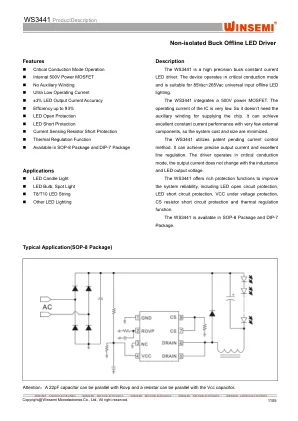

WS3441A 产品描述

注意:1.我们强烈建议客户在购买我们的产品时仔细检查商标,如果有任何问题,请随时与我们联系。2.电路设计时请不要超过设备的绝对最大额定值。3.Winsemi Microelectronics Co., Ltd 保留对本规格书进行更改的权利,如有更改,恕不另行通知。

LISA M. LUST 霍尼韦尔国际 12001 State Hwy。......

拥有 23 年光学、电磁和射频电路设计经验,应用于原子和离子传感器、光子器件、MEMS 传感器、有源天线和低可观测材料的开发。擅长将技术从概念转化为生产,并曾赢得数百万美元的项目。经验领域包括:电磁学/射频和微波设计

DX6210 高功率因数、低 THD、隔离离线 LED 控制器

注意:1.我们强烈建议客户在购买我们的产品时仔细检查商标,如果有任何问题,请随时与我们联系。2.电路设计时请不要超过设备的绝对最大额定值。3.Winsemi Microelectronics Co., Ltd 保留对本规格书进行更改的权利,如有更改,恕不另行通知。

非隔离降压离线 LED 驱动器

注意:1.我们强烈建议客户在购买我们的产品时仔细检查商标,如果有任何问题,请随时与我们联系。2.电路设计时请不要超过设备的绝对最大额定值。3.Winsemi Microelectronics Co., Ltd 保留对本规格书进行更改的权利,如有更改,恕不另行通知。

你一直想知道的有关量子电路的一切

量子计算电路的开发受到量子算法激增的推动,这些算法有望比经典算法实现超多项式因子的加速。所开发的量子算法有可能影响数论、加密、科学计算等领域 [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16]。量子算法的设计仍然是一个活跃的研究领域,新算法不断出现在文献中(有关量子算法的代表性列表,请参阅 [17])。为了实现这些提议的量子算法的潜在性能提升,必须在量子硬件上实现它们。IBM 或 Honeywell 等实体开发的量子计算机就是可用于实现量子算法的量子硬件平台的一个例子 [18] [19] [20] [21] [22]。为了在这些硬件平台上实现量子算法,我们需要由量子电路组成的量子数据通路系统。在本文中,我们将介绍量子电路的设计和资源成本评估。这些量子电路由量子门网络组成。IBM 和 Honeywell 等实体开发的量子机支持基于门的量子计算。基于门的量子电路设计可用于容错量子计算和量子电路设计自动化 [23] [24] [25] [26] [27] [28] [16] [29]。每个量子门代表一个量子力学操作。因此,使用量子电路的设计者必须应对新的特性和挑战。例如,量子电路是一对一的,所有信息都被保留。用于实现量子算法的量子电路设计引起了研究人员的关注。已经提出了用于基本功能(例如基本算术功能(例如加法或除法))的电路,例如 [30] [31] [32] [33] [34] [35] [36] [37]。这些基本电路被用作更复杂的数据通路系统的构建块,例如用于科学计算、图像处理或机器学习的高级数学函数 [38] [39] [40] [12] [41] [42] [43]。