机构名称:

¥ 1.0

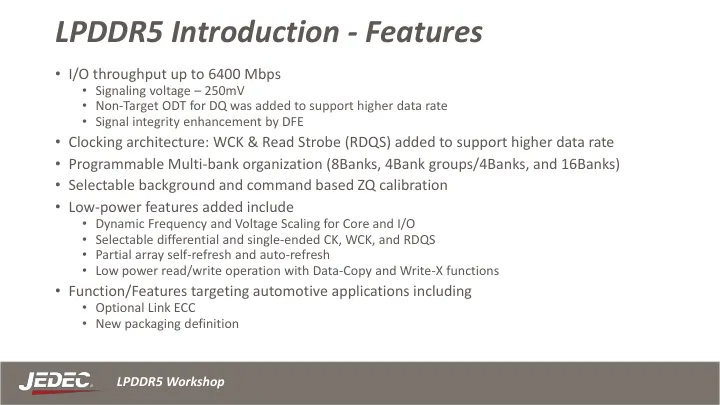

• Signaling voltage – 250mV • Non-Target ODT for DQ was added to support higher data rate • Signal integrity enhancement by DFE • Clocking architecture: WCK & Read Strobe (RDQS) added to support higher data rate • Programmable Multi-bank organization (8Banks, 4Bank groups/4Banks, and 16Banks) • Selectable background and command based ZQ calibration • Low-power features added include

简介LPDDR5研讨会