机构名称:

¥ 1.0

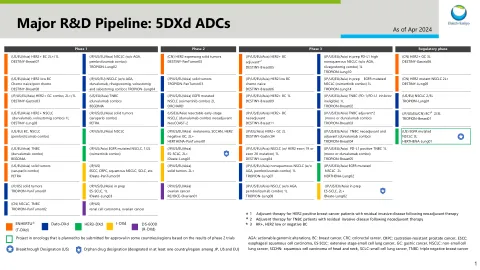

摘要 - 解码算法允许以增加面积的成本实现极高的吞吐量。查找表(LUTS)可用于替换其他作为电路实现的功能。在这项工作中,我们显示了通过在独立的解码器中精心制作的LUTS代替逻辑块的影响。我们表明,使用LUTS改善关键性能指标(例如,区域,吞吐量,潜伏期)可能比预期更具挑战性。我们提出了三种基于LUT的解码器的变体,并详细描述了它们的内部工作以及电路。基于LUT的解码器与常规展开的解码器进行了比较,该解码器采用固定点表示数字,具有可比的误差校正性能。简短的系统极性代码被用作说明。所有由此产生的展开解码器均显示能够在28 nm FD-SOI技术中以1.4 GHz至1.5 GHz的时钟进行少于10 Gbps的信息吞吐量。与常规展开的解码器相比,我们的基于LUT的解码器的最佳变体可将面积的需求降低23%,同时保留可比的错误校正性能。

基于极地代码的查找表的展开和管道解码器