机构名称:

¥ 17.0

•双CPU子系统-160-MHz(最大)32-BITARM®Cortex®-M4F CPU,带有•单周期乘以•单精制浮点单位(FPU)•存储器保护单元(MPU) - 100-MHz(MAX)32位甲型Cortex®M0+CORTEX®M0+CORTEX®M0+ CORTER••单位•固定••单位••单位••单位••速度•连接• controllers • Peripheral DMA controller #0 (P-DMA0) with 92 channels • Peripheral DMA controller #1 (P-DMA1) with 44 channels • Memory DMA controller #0 (M-DMA0) with 4 channels • Integrated memories - 4160 KB of code-flash with an additional 128 KB of work-flash • Read-While-Write (RWW) allows updating the从其执行代码时code-flash/work-flash•单银行和双银行模式(专门用于空气上的固件更新[fota])•通过SWD/JTAG接口进行闪存编程-512 kb的SRAM,可选保留粒度•Crypto Engine [1]

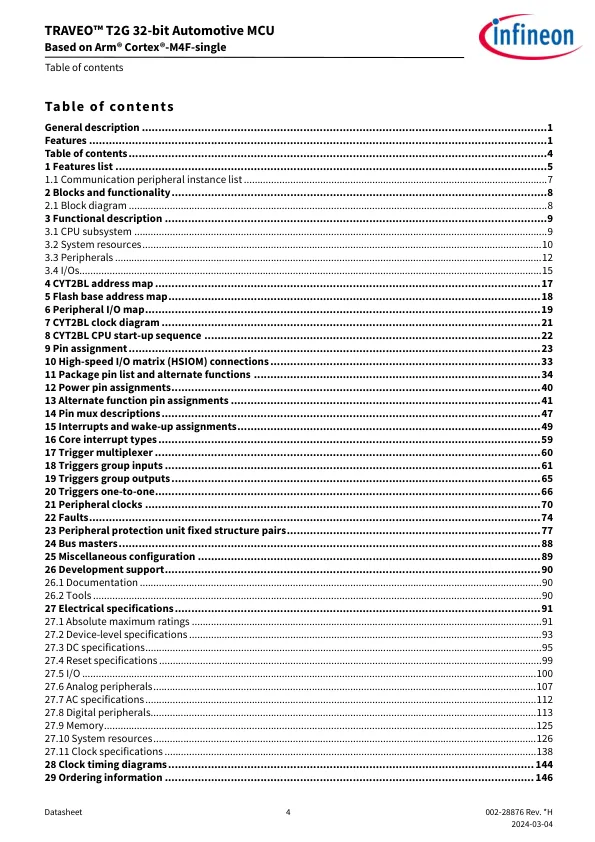

CYT2BL -Traveo™T2G 32位汽车MCU