机构名称:

¥ 5.0

� 高性能浮点数字信号处理器 (DSP) – TMS320C30-50 (5 V) 40 纳秒指令周期时间 275 MOPS、50 MFLOPS、25 MIPS – TMS320C30-40 (5 V) 50 纳秒指令周期时间 220 MOPS、40 MFLOPS、20 MIPS – TMS320C30-33 (5 V) 60 纳秒指令周期时间 183.3 MOPS、33.3 MFLOPS、16.7 MIPS – TMS320C30-27 (5 V) 74 纳秒指令周期时间 148.5 MOPS、27 MFLOPS、13.5 MIPS � 32 位高性能 CPU � 16/32 位整数和 32/40 位浮点运算 � 32 位指令字,24 位地址 � 两个 1K × 32 位单周期双访问片上 RAM 块 � 一个 4K × 32 位单周期双访问片上 ROM 块 � 片上存储器映射外设: – 两个串行端口 – 两个 32 位计时器 – 单通道直接存储器访问 (DMA) 协处理器,用于并发 I/O 和 CPU 操作

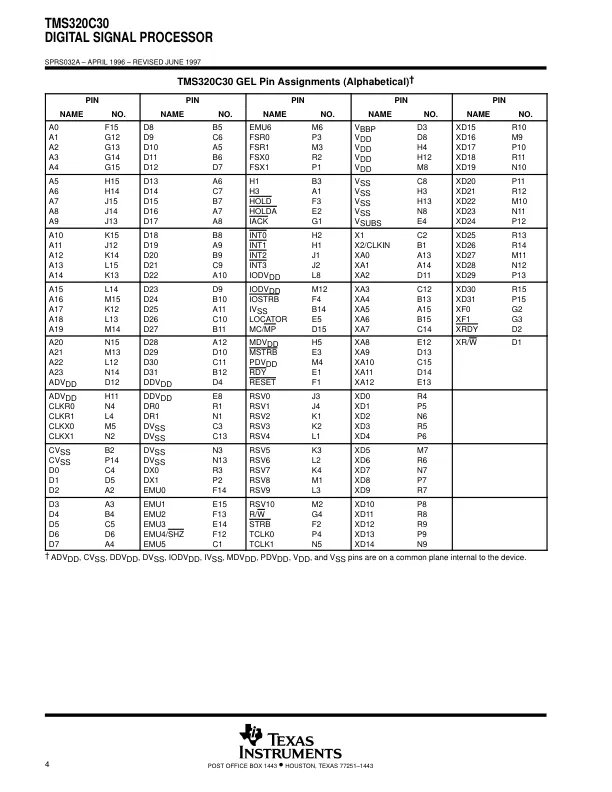

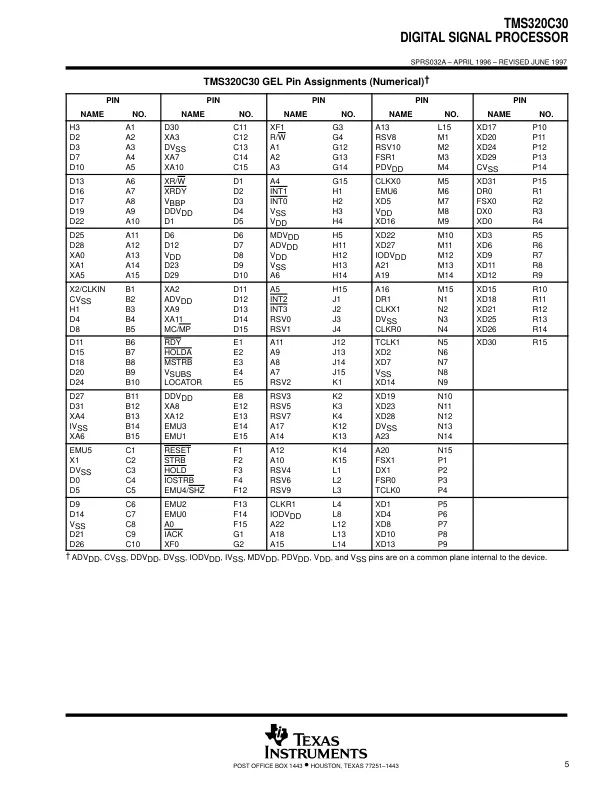

TMS320C30 数字信号处理器