XiaoMi-AI文件搜索系统

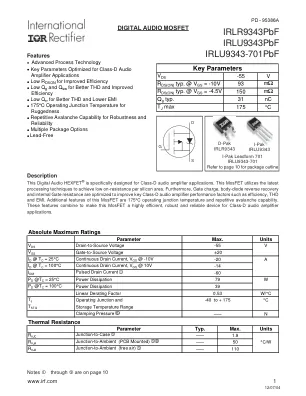

World File Search SystemIRLR9343PbF IRLU9343PbF IRLU9343-701PbF

关于重复性雪崩曲线的注释,图 14、15:(有关更多信息,请参阅 www.irf.com 上的 AN-1005)1.雪崩故障假设:纯粹的热现象和故障发生在远超过 T jmax 的温度下。这已针对每种零件类型进行了验证。2.只要不超过 T jmax,就可以在雪崩中安全运行。3.以下公式基于图 17a、17b 中所示的电路和波形。4.P D (ave) = 每个雪崩脉冲的平均功率耗散。5.BV = 额定击穿电压(1.3 倍因数表示雪崩期间电压增加)。6.I av = 允许的雪崩电流。7.∆ T = 允许的结温升高,不得超过 T jmax(在图 14、15 中假设为 25°C)。t av = 雪崩平均时间。D = 雪崩占空比 = t av ·f Z thJC (D, t av ) = 瞬态热阻,见图 11) P D (ave) = 1/2 ( 1.3·BV·I av ) = � � T/ Z thJC I av = 2 � T/ [1.3·BV·Z th ] E AS (AR) = P D (ave) ·t AV

微型机械泵回路建模和设计...

随着星载传感器的小型化,预计小型卫星将使用更强大的有效载荷。因此,需要新的热概念来应对日益增加的热耗散和负面影响。本文提出了一种新的热控制概念,以对具有功率耗散问题的小型卫星进行热标准化,使其在热方面不受轨道的影响。这种新的热设计概念是微型机械泵回路 (MPL)。微型 MPL 的设计考虑了立方体卫星及其子系统的要求,从而确保其与小型卫星和各种任务的兼容性。该系统的核心是荷兰航空航天中心 (NLR) 开发的多并联微型泵 (MPMP)。这种泵概念提供了一种低质量、高可靠性的 MPL 解决方案。随后,本文描述了回路和泵的概念,并给出了微型泵的测试结果。Mini-MPL 也在 Matlab 中建模,以支持 MPL 系统设计权衡。本文描述了该模型,并展示了建模结果,并将其纳入了详细的工作流体选择中。最后,通过与传统热设计方案的比较,阐明了该系统的优点和缺点。本文最后展望了进一步的发展和 mini-MPL 应用。

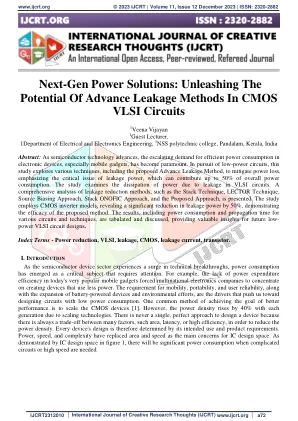

下一代功率解决方案:释放CMOS

1 Veena Vijayan 1来宾讲师,电气和电子工程的1台,1 NSS理工学院,潘达拉姆,喀拉拉邦,喀拉拉邦,印度摘要:随着半导体技术的进步,随着半导体技术的进步,对电子设备有效的电力消耗的需求不断提高,尤其是电子设备,尤其是移动装备,已成为最重要的。在追求低功率电路时,本研究探讨了各种技术,包括拟议的预先泄漏方法,以减轻功率损失,强调泄漏功率的关键问题,这可以占总体电力消耗的50%。该研究检查了由于VLSI电路中泄漏引起的功率耗散。列出了对泄漏减少方法的全面分析,例如堆栈技术,Lector技术,源偏置方法,堆栈Onofic方法和建议的方法。该研究采用CMOS逆变器模型,揭示了泄漏功率的显着降低50%,证明了该方法的功效。列出了和讨论的结果,包括各种电路和技术的功耗和传播时间,为将来的低功率VLSI电路设计提供了宝贵的见解。索引项 - 功率降低,VLSI,泄漏,CMO,泄漏电流,晶体管。

设计和实施低功耗...

移动,电池电力系统(例如蜂窝电话,个人数字助手等)不断增长的市场要求设计具有低功率耗散的微电子电路。更一般而言,随着芯片的密度,大小和复杂性继续增加,提供足够冷却的困难可能会增加大量成本,或者限制使用这些集成电路的计算系统的功能。在过去十年中,已经提出了几种设计低功率电路的技术,方法和工具。但是,其中只有少数在当前设计流中找到了自己的方式[1]。在CMOS电路中,有三个主要的功率耗散来源。这些是开关功率,短路电源和泄漏功率。开关功率是由于电路驱动的充电和排放电容器。短路功率是由同时进行PMOS/NMOS晶体管对时产生的短路电流引起的。最后,泄漏功率起源于底物注入和子阈值效应。导致泄漏功率增加的主要原因之一是子阈值泄漏功率的增加。当技术尺寸缩小时,电源电压和阈值电压也会缩小。子阈值泄漏功率随着阈值电压的降低而成倍增加。堆栈方法,强制NMO,强制PMO和困倦的门将方法是一些泄漏电流减少方法[2]。

IRLR9343PbF IRLU9343PbF IRLU9343-701PbF

重复雪崩曲线说明,图 14、15:(有关更多信息,请参见 www.irf.com 上的 AN-1005)1. 雪崩故障假设:纯粹的热现象,故障发生在远超过 T jmax 的温度下。这适用于每种零件类型。2. 只要不超过 T jmax,就可以在雪崩中安全运行。3. 以下公式基于图 17a、17b 所示的电路和波形。4. PD (ave) = 每个雪崩脉冲的平均功率耗散。5. BV = 额定击穿电压(1.3 倍因子考虑雪崩期间的电压增加)。6. I av = 允许的雪崩电流。7. ∆ T = 允许的结温上升,不得超过 T jmax(在图 14、15 中假设为 25°C)。 t av = 雪崩平均时间。D = 雪崩占空比 = t av ·f Z thJC (D, t av ) = 瞬态热阻,见图 11) PD (ave) = 1/2 ( 1.3·BV·I av ) = T/ Z thJC I av = 2 T/ [1.3·BV·Z th ] E AS (AR) = PD (ave) ·t av

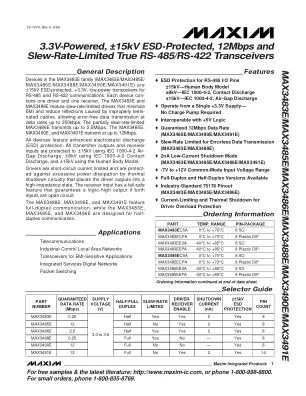

MAX3483E/MAX3485E/MAX3486E/MAX3488E/MAX3490E ...

MAX3483E 系列器件 (MAX3483E/MAX3485E/ MAX3486E/MAX3488E/MAX3490E/MAX3491E) 是具有 ±15kV ESD 保护、+3.3V、低功耗收发器,适用于 RS-485 和 RS-422 通信。每个器件包含一个驱动器和一个接收器。MAX3483E 和 MAX3488E 具有斜率限制驱动器,可最大程度降低 EMI 并减少由电缆端接不当引起的反射,从而允许以高达 250kbps 的数据速率进行无错误数据传输。部分斜率限制的 MAX3486E 传输速率高达 2.5Mbps。MAX3485E、MAX3490E 和 MAX3491E 的传输速率高达 12Mbps。所有器件均具有增强的静电放电 (ESD) 保护功能。所有发射器输出和接收器输入均采用 IEC 1000-4-2 气隙放电保护 ±15kV,采用 IEC 1000-4-2 接触放电保护 ±8kV,采用人体模型保护 ±15kV。驱动器具有短路电流限制,并通过热关断电路防止过大的功率耗散,该电路将驱动器输出置于高阻抗状态。接收器输入具有故障安全功能,当两个输入都开路时,可保证逻辑高输出。MAX3488E、MAX3490E 和 MAX3491E 具有全双工通信功能,而 MAX3483E、MAX3485E 和 MAX3486E 则设计用于半双工通信。

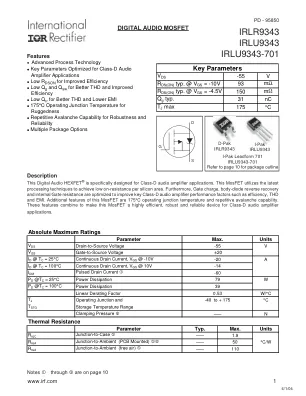

IRLR9343 IRLU9343 IRLU9343-701

关于重复雪崩曲线的注释,图 14、15:(有关更多信息,请参见 www.irf.com 上的 AN-1005)1. 雪崩故障假设:纯粹的热现象和故障发生在远超过 T jmax 的温度下。这针对每种零件类型均进行了验证。2. 只要不超过 T jmax,就可以在雪崩中安全运行。3. 以下公式基于图 17a、17b 所示的电路和波形。4. P D (ave) = 每个雪崩脉冲的平均功率耗散。5. BV = 额定击穿电压(1.3 倍因子考虑雪崩期间的电压增加)。6. I av = 允许的雪崩电流。7. ∆ T = 允许的结温上升,不得超过 T jmax(在图 14、15 中假设为 25°C)。 t av = 雪崩平均时间。D = 雪崩占空比 = t av ·f Z thJC (D, t av ) = 瞬态热阻,见图 11) P D (ave) = 1/2 ( 1.3·BV·I av ) = � � T/ Z thJC I av = 2 � T/ [1.3·BV·Z th ] E AS (AR) = P D (ave) ·t av

低区域高速组合乘数...

摘要: - 在数字图像处理中,中位过滤器用于减少图像中的噪声。中间过滤器考虑了图像中的每个像素,并用邻域像素的中位数代替嘈杂的像素。中值是通过对像素进行排序计算的。排序依次由比较器组成,该比较器包括加法器和乘数。乘法是算术计算系统中的基本操作,用于许多DSP应用程序(例如FIR滤波器)。加法电路用作乘数电路中的主要组件。随身携带阵列(CSA)乘数是通过基于多重逻辑的建议的加法单元格设计的。提出的加法电路是通过使用香农定理设计的。将乘数电路进行了示意图,并使用VLSI CAD工具生成它们的布局。模拟了所提出的基于加法器的乘数电路,并将结果与CPL和其他基于Shannon的加法器细胞设计的电路进行了比较。通过使用90nm特征大小和各种电源电压来模拟所提出的基于加法器的乘数电路。Shannon Full Adder Cource的乘数电路比其他已发表的结果在功率耗散和面积方面提供了更好的性能,这是由于Shannon Adder电路中使用的晶体管数量较少。

平面射频磁控等离子体中的电子动力学:I.霍尔加热机制和µ模式

摘要 研究了低压射频 (RF) 驱动磁增强电容耦合等离子体中的电子动力学和功率吸收机制。重点研究的装置是一个几何不对称的圆柱形磁控管,轴向具有径向不均匀的磁场,径向具有电场。使用冷等离子体模型和单粒子形式对动力学进行分析研究,并使用内部能量和电荷守恒粒子室内/蒙特卡罗碰撞代码 ECCOPIC1S-M 对动力学进行数值研究。发现动力学与未磁化的参考放电有显著不同。在通电电极前方的磁化区域中,在鞘层膨胀期间会产生增强电场,在鞘层塌陷期间会产生反向电场。这两个场都是确保放电维持电子传输以抵抗磁场限制效应所必需的。相应的方位 E × B 漂移可以将电子加速到非弹性能量范围,从而产生一种新的射频功率耗散机制。它与霍尔电流有关,性质上不同于欧姆加热,以前的文献中将其归类为欧姆加热。这种新的加热方式有望在许多磁化电容耦合放电中占主导地位。建议将其称为“µ 模式”,以将其与其他加热模式区分开来。

分数-N的修改脉冲吞咽频率分隔器...

分数-N频率合成器的设计已成为流行的研究领域。分数-N频率合成器已被广泛,成功地用于需要高精度频率源的范围,例如全球导航卫星系统(GNSS)RF接收器,高精度基站和手机RF收发器芯片等。作为分数-N频率合成器的关键组成部分,频率分隔线提出了更高的要求。因此,高功耗速度和低功耗分数分隔器是高度想要的[1,2,2,3,4,5,6,7,8,9,11,11,11,11,12,13,13,14,15,15,16,17,18,18,19,20]。脉冲吞咽频率分隔线的工作速度限制取决于MC信号(τmc)的延迟时间[1,2,3,20,21,22,23,24,25,26]。在[1]中,采用了d频流以延迟MC,以减少τmc。虽然这种结构固有地具有一个不需要的分裂比例,因为MC信号的集合和重置是由不同的信号触发的。为了解决此问题,在[2,3]中的一个信号触发了MC信号。但是,这两个架构分别导致SR闩锁的可能性不良,并分别增加τmc。在[21,22]中删除了SR闩锁,以避免[2]中提到的问题。此外,所有其他问题,也列出为:保留MC方案,依赖模量的分隔线延迟,操作速度,外部脉冲生成电路和MC信号延迟误差,也被克服了这两个文献。尽管如此,电路的复杂性和功率耗散