机构名称:

¥ 1.0

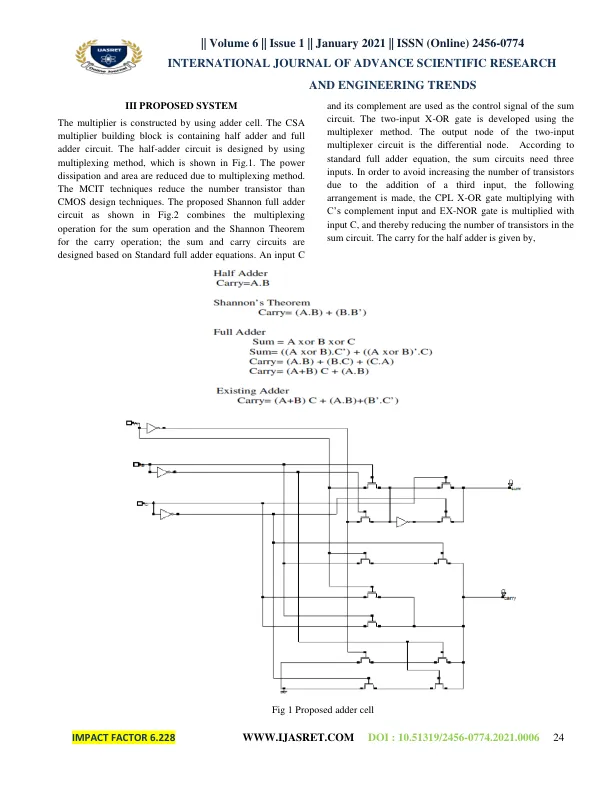

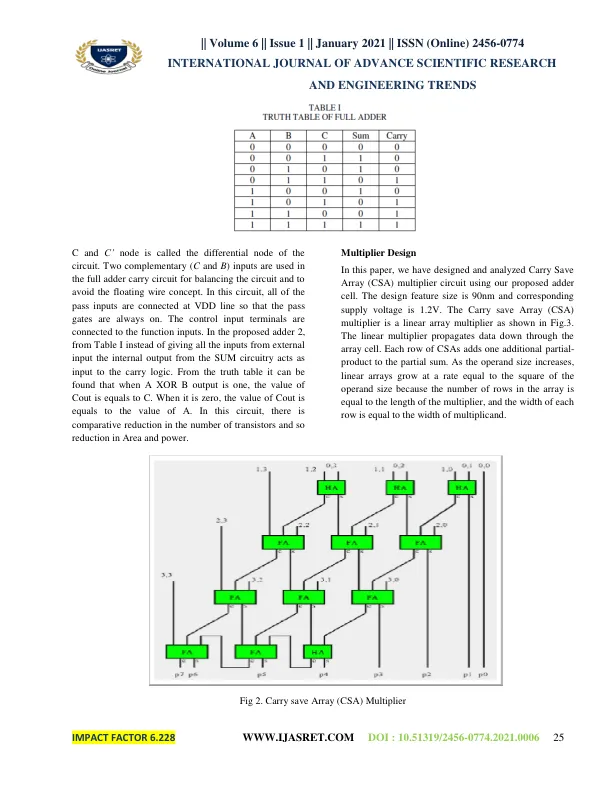

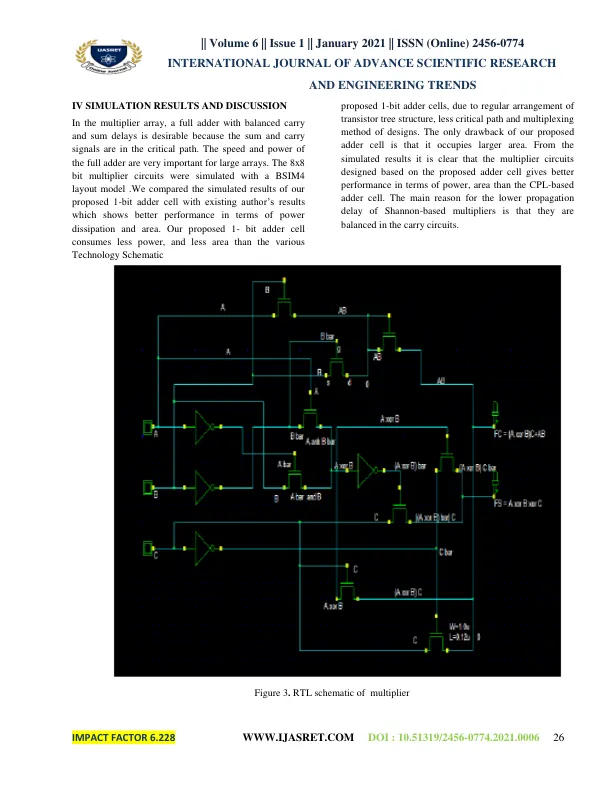

摘要: - 在数字图像处理中,中位过滤器用于减少图像中的噪声。中间过滤器考虑了图像中的每个像素,并用邻域像素的中位数代替嘈杂的像素。中值是通过对像素进行排序计算的。排序依次由比较器组成,该比较器包括加法器和乘数。乘法是算术计算系统中的基本操作,用于许多DSP应用程序(例如FIR滤波器)。加法电路用作乘数电路中的主要组件。随身携带阵列(CSA)乘数是通过基于多重逻辑的建议的加法单元格设计的。提出的加法电路是通过使用香农定理设计的。将乘数电路进行了示意图,并使用VLSI CAD工具生成它们的布局。模拟了所提出的基于加法器的乘数电路,并将结果与CPL和其他基于Shannon的加法器细胞设计的电路进行了比较。通过使用90nm特征大小和各种电源电压来模拟所提出的基于加法器的乘数电路。Shannon Full Adder Cource的乘数电路比其他已发表的结果在功率耗散和面积方面提供了更好的性能,这是由于Shannon Adder电路中使用的晶体管数量较少。

低区域高速组合乘数...

主要关键词