XiaoMi-AI文件搜索系统

World File Search System烟草微生物群落结构和挥发性化合物在雪茄堆叠发酵过程中的相互作用分析

在CTL的生长和农业发酵阶段,相关的酶活性发生了显着变化(Banozic等,2020)。在CTLS生长过程中积累的淀粉,纤维素和果胶在农业发酵阶段逐渐降解,然后转化为CTLS的香气前体和VFC(Zhang等,2021)。在这一点上,尽管烟气仍然相对粗糙,并且还需要进一步酸化CTL的主要香气,并且需要进一步酸化,而杂物,苦味,苦味和其他不良口味,除了通过堆叠发酵来减少刺激性,以进一步富含CTL的质量并提高质量的质量(Liu F. F. F. F. F. et al 20222222222222)。堆叠发酵是雪茄生产过程中的工业发酵阶段,并且与大分子物质在生长和农业发酵过程中的快速降解相比,主要堆叠发酵是主要转化小分子物质和VFC。VFCS的含量随微生物和相关酶的功能而变化,尽管类型的变化很小,并且可以实现增加香气,减少其他气体的效果,并使烟气酸化(Liu F. F. F. et al。

CIS 堆叠技术

灵敏度 - 数字成像 - 像素 - 量子效率 - 复位 - 正向偏置 - 区域板 - 通道电位 - 全帧成像器 - PPD - 采样频率 - 光子散粒噪声 - VGA - 产量 - 暗固定模式噪声 - 反向偏置二极管 - 收集效率 - 逐行扫描 - 动态范围 - 薄膜干涉 - 固定光电二极管 - 光谱灵敏度 - 饱和电压 - 双线性成像器 - 光子传输曲线 - 行间传输图像传感器 - 电荷耦合器件 - 微透镜 - 暗电流散粒噪声 - E SD - 条纹滤波器 - 数码相机 - 拼接 - 高斯分布 - 硅 - 热噪声 - 传感器结构 - 亮度 - 浮动扩散放大器 - 转换因子 - 闪烁 - MOS 电容 - 辐射单位 - 移位寄存器 - 带隙 - 黄色 - 补色 - 光电门 - 列放大器 - 纹波时钟 - 反转层 - CMOS 成像器 - 对数响应 - 普朗克常数 - 电荷泵 - 阈值电压 - 埋通道 CCD - 暗电流 - 噪声等效曝光 - MSB - 转换因子 -缺陷像素校正 - 边缘场 - 分辨率 - 双相传输 - 正透镜 - 角响应 - PRNU - 波长 - 帧传输成像器 - 电荷注入装置 - 测试 - 通道定义 - 摄像机 - 光晕 - 隔行扫描 - 彩色滤光片 - 自动白平衡 - 虚拟相位 - 拖尾 - 单斜率 ADC - 表面电位 - 耗尽层 - 垂直防光晕 - 多相钉扎 - 电子快门 - PAL - 埃普西隆 - 相关双采样 - 蓝色 - CIF - 洋红色 - 填充因子 - 延迟线 - 线性响应 - 规格 - 结深 - 复位噪声 - 线性图像传感器 - 光学低通滤波器 - 二氧化硅 - 光电二极管 - 勒克斯 - 闪光 ADC - 定时抖动 - 拥有成本 - 封装 - 光刻 - 有源像素传感器 - DSP - 积分时间 - 三相传输 - 光子通量 - 晶圆级封装 - 电荷泵 - 滤光轮 - 有效线时间 - 吸收深度 - 玻尔兹曼常数 - 弱反转 - LSB - 水平消隐 - 光栅滤波器 - 帧抓取器 - 原色 - 拜耳模式- 缩放 - 功耗 - 单色仪 - 模拟数字转换 - 光固定模式噪声 - 无源像素传感器 - 彩色棱镜 - SGA - 氮化硅 - 温度依赖性 - 负透镜 - sigma delta ADC - 混叠 - 插值 - 传输效率 - F 数 - 红色 - 动态像素管理 - 栅极氧化物 - 热漂移 - 热噪声 - 扩散 MTF - 有源像素传感器 - 泄漏器 - 1/f 噪声 - 青色 - 信噪比 - 孔径比 - 奈奎斯特频率 - 非隔行扫描 - 像素内存储器 - 四相传输 - 技术 - kTC 噪声 - 辐射损伤 - 离子注入 - MOS 晶体管 - 内透镜 - 光度单位 - 表面通道 CCD - 延时和集成成像器 - 宽高比 - 绿色 - NTSC - 单芯片相机 -可见光谱 - 调制传递函数 - 同步快门 - 马赛克滤光片 - 背面照明 - 色彩串扰 - 量化噪声 - 逐次逼近 ADC - 压缩 - 漏极 - 多晶硅 - 堆叠 - 光子转换 - 飞行时间 - 吸收系数 - DIL - 收集体积 - 孔 - 四线性成像器 - 单相传输 - 填充和溢出 - 收集效率 - 垂直消隐 - 源极跟随器 - 雪崩倍增 - 辐射 - 横向防晕 - 晶圆上测试 - 自感场 - 自动曝光 - 泊松分布 - 电荷复位 - 伽马

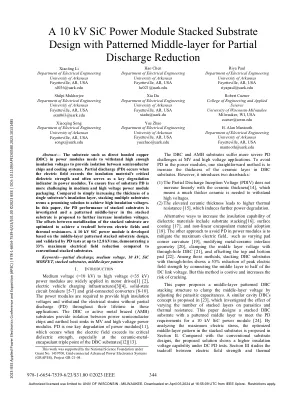

10 kV SiC 功率模块堆叠基板设计,具有图案化中间层,可减少局部放电

摘要 — 电源模块中的直接键合铜 (DBC) 等基板需要承受足够高的绝缘电压,以提供半导体芯片和冷却系统之间的隔离。当电场超过绝缘材料的临界介电强度时,就会发生局部放电 (PD),并且它通常是电源模块中的关键退化指标。确保在中高压电源模块封装中没有基板 PD 更具挑战性。与简单地增加单个基板绝缘层的厚度相比,堆叠多个基板似乎是实现高绝缘电压的一种有前途的解决方案。本文研究了堆叠基板的 PD 性能,并提出了在堆叠基板中采用图案化中间层以进一步提高绝缘电压。优化了堆叠基板的金属化之间的偏移量,以实现电场和热阻之间的权衡。基于中间层图案化堆叠基板设计开发了10 kV SiC 功率模块,并通过高达 12.8 kVrms 的 PD 测试验证,与传统堆叠基板相比,最大电场降低了 33%。

可解释的大脑图的堆叠回归和结构性方差分配

将与复杂刺激相关的大脑活动与2的不同特性相关联,刺激是构建功能性脑图的强大方法。然而,3当刺激是自然主义时,它们的性质通常是相关的(例如,自然图像的视觉和4个语义特征,或用作图像特征的卷积神经网络5的不同层)。相关性能可以充当混杂因素6,并使大脑图的解释性复杂化,并可能影响统计估计器的7个鲁棒性。在这里,我们根据提出的两种方法提出了一种大脑映射8的方法:堆叠不同的编码模型和结构化9方差分配。我们的堆叠算法结合了编码模型,每个模型都将10用作输入一个描述不同刺激属性的特征空间。算法11学会预测体素的活性,作为不同12个编码模型的输出的线性组合。我们表明,由此产生的组合模型可以更好或至少与单个编码模型更好或至少预测13个大脑活动。此外,线性组合的14个权重很容易解释;它们显示了预测体素的每个特征空间的重要性15。然后,我们将堆叠模型构建到16个引入结构化方差分区,这是一种新型的方差分区,考虑了17个特征之间的已知关系。我们验证了我们的模拟方法,展示其大脑在fMRI数据上的21个潜力,并发布Python软件包。24我们的方法限制了假设空间的18个大小,并使我们能够提出有关特征空间和大脑区域之间相似性19的有针对性问题,即使在20个特征空间之间存在相关性的情况下。我们的方法对于有兴趣将大脑活动与神经网络的不同层(23)或其他类型的相关特征空间对齐的研究人员有用。

研究基于堆叠的源沟槽TFET

摘要:为了检测生物分子,提出了基于介电调节的堆叠源沟槽闸门隧道效果晶体管(DM-SSTGTFET)的生物传感器。堆叠的源结构可以同时使状态电流较高,并且较低的状态电流较低。沟槽栅极结构将增加隧道区域和隧道概率。技术计算机辅助设计(TCAD)用于对拟议的结构化生物传感器的灵敏度研究。结果表明,DM-SSTGTFET生物传感器的当前灵敏度可以高达10 8,阈值电压灵敏度可以达到0.46 V,亚阈值秋千灵敏度可以达到0.8。由于其高灵敏度和低功耗,该提议的生物传感器具有很高的前景。

计划:可堆叠高管 M.Tech AI

为迎合NEP2020可堆叠课程理念,针对在职专业人士的举措。课程在周末或工作日晚上以在线模式进行,学生以同步交互式视听模式上课。每学期的学分要求灵活。学生每学期可以注册任意数量的课程(满足最低和最高学分要求) 课程选修课和开放选修课可从各院系和学院提供的各种课程中选择,包括计算机科学与工程、电气工程、AIDE 学院、数学、机械工程 面向行业的课程,如 ML-Ops 和 DL-Ops 录制的讲座和教学材料可在线获取 课程管理和讨论可通过广泛使用的工具(如 Google Classroom、Piazza 和 Moodle)进行 每学期有两个强制性的接触周 学生必须参加讲师的讲座和讨论会,参加线下评估,并亲身体验 IIT 环境 接触周可能会在偏远地区组织,具体取决于更高的需求 学生可以完成他们的 M. Tech。项目(由政府资助。资助机构和行业)跨部门的最先进研究课题

文章结构,氮化钛电极的氧气含量和电性能X /LA:HFO 2 /TIN X堆叠在Sio 2 /si 2 /si < /div>

TRON能量损失光谱被彻底考虑。研究表明,在底部电极中的氧气浓度较高(约14.2±0.1 at。%)与顶部电极相比(约11.4±0.5 at。%)。以下平均化学计量公式为锡0。52 o 0。20上衣和锡0。54 O 0。 26底部和底部电极的底部。 由于血浆中的氧杂质与SIO 2和HFO 2的扩散相比,血浆中的氧气量不足。 这种不对称性,以及在Si底物上生长的样品的结果表明,与从SIO 2底物和PEALD生长过程中从SIO 2底物和HFO 2介电介质的扩散相比,与血浆本身的氧杂质相比是一个较小的部分。 我们观察到HF氧化物层和Ti nitride Electrodes以及SIO 2界面之间的界面上的TIO 2存在。 EELS分析导致底部锡X O Y的带隙范围为2.2至2.5 eV,而顶部锡X O Y的带隙范围为1.7-2.2 eV,使用光吸收光谱与顶部Tin X电极(1.6±01 eV)上的结果公平吻合。 测量板电阻,电阻率和温度系数通过在20到100°C的顶部锡x o y电极上的四点探头的电阻系数对应于半导体的典型值。54 O 0。26底部和底部电极的底部。由于血浆中的氧杂质与SIO 2和HFO 2的扩散相比,血浆中的氧气量不足。这种不对称性,以及在Si底物上生长的样品的结果表明,与从SIO 2底物和PEALD生长过程中从SIO 2底物和HFO 2介电介质的扩散相比,与血浆本身的氧杂质相比是一个较小的部分。我们观察到HF氧化物层和Ti nitride Electrodes以及SIO 2界面之间的界面上的TIO 2存在。EELS分析导致底部锡X O Y的带隙范围为2.2至2.5 eV,而顶部锡X O Y的带隙范围为1.7-2.2 eV,使用光吸收光谱与顶部Tin X电极(1.6±01 eV)上的结果公平吻合。测量板电阻,电阻率和温度系数通过在20到100°C的顶部锡x o y电极上的四点探头的电阻系数对应于半导体的典型值。

自下而上制造和表征用于电子应用的自对准栅极堆叠_最终版

1 S. Datta、S. Dutta、B. Grisafe、J. Smith、S. Srinivasa 和 H. Ye,IEEE Micro 39,8 (2019)。2 T. Bryllert、L.-E. Wernersson、T. Löwgren 和 L. Samuelson,Nanotechnology 17,S227 (2006)。3 D. Akinwande、N. Petrone 和 J. Hone,Nat Commun 5,5678 (2014)。4 R. Chen、H. Kim、PC McIntyre、DW Porter 和 SF Bent,Applied Physics Letters 86 (2005)。5 R. Chen、H. Kim、PC McIntyre 和 SF Bent,Applied Physics Letters 84,4017 (2004)。 6 S. Seo、BC Yeo、SS Han、CM Yoon、JY Yang、J. Yoon、C. Yoo、HJ Kim、YB Lee、SJ Lee、JM Myoung、HB Lee、WH Kim、IK Oh 和 H. Kim,ACS Appl Mater Interfaces 9,41607 (2017)。7 KJ Park、JM Doub、T. Gougousi 和 GN Parsons,Applied Physics Letters 86 (2005)。8 FS Minaye Hashemi、C. Prasittichai 和 SF Bent,ACS Nano 9,8710 (2015)。9 WH Kim、HBR Lee、K. Heo、YK Lee、TM Chung、CG Kim、S. Hong、J. Heo 和 H. Kim,Journal of the Electrochemical Society 158,D1 (2011)。 10 H. Kim,ECS Transactions 16, 219 (2008)。11 R. Wojtecki、J. Ma、I. Cordova、N. Arellano、K. Lionti、T. Magbitang、TG Pattison、X. Zhao、E. Delenia 和 N. Lanzillo,ACS applied materials & interface 13, 9081 (2021)。12 E. Färm、M. Kemell、M. Ritala 和 M. Leskelä,The Journal of Physical Chemistry C 112, 15791 (2008)。13 E. Färm、M. Kemell、E. Santala、M. Ritala 和 M. Leskelä,Journal of The Electrochemical Society 157 (2010)。 14 A. Sinha、DW Hess 和 CL Henderson,《真空科学与技术杂志 B:微电子学和纳米结构》24(2006 年)。15 V. Suresh、MS Huang、MP Srinivasan、C. Guan、HJ Fan 和 S. Krishnamoorthy,《物理化学杂志 C 116,23729》(2012 年)。16 A. Sinha、DW Hess 和 CL Henderson,《真空科学与技术杂志 B:微电子学和纳米结构》25(2007 年)。17 TG Pattison、AE Hess、N. Arellano、N. Lanzillo、S. Nguyen、H. Bui、C. Rettner、H. Truong、A. Friz 和 T. Topuria,《ACS nano 14,4276》(2020 年)。 18 M. Fang 和 JC Ho,ACS Nano 9,8651(2015)。19 AJ Mackus、AA Bol 和 WM Kessels,Nanoscale 6,10941(2014)。20 MJ Biercuk、DJ Monsma、CM Marcus、JS Becker 和 RG Gordon,Applied Physics Letters 83,2405(2003)。21 AT Mohabir、G. Tutuncuoglu、T. Weiss、EM Vogel 和 MA Filler,ACS nano(2019)。22 E. Bassous 和 A. Lamberti,Microelectronic Engineering 9,167(1989)。23 C. Ton-That、A. Shard、D. Teare 和 R. Bradley,Polymer 42,1121(2001)。 24 P. Louette、F. Bodino 和 J.-J. Pireaux,表面科学光谱 12,69 (2005)。25 A. Richard,法拉第讨论 98,219 (1994)。

MoS2堆叠纳米片场效应晶体管的模拟

根据2021年国际器件与系统路线图(IRDS),环栅晶体管(GAA)将从3nm技术节点开始取代FinFET,并应用于1nm技术节点。下一步,尺寸缩小的目标不仅是降低漏电,更重要的是降低功率,而包括三维异质集成在内的三维垂直架构将成为降低功耗的主流技术。要延续摩尔定律,不仅需要通过器件尺寸缩小来提高电路集成度,还需要降低功率和提高开关速度。堆叠式NSFET具有更好的静电完整性、短沟道免疫力,因此具有更好的功率缩放性能,是未来亚3nm技术节点的有希望的候选者[1−3]。