XiaoMi-AI文件搜索系统

World File Search SystemPQ-HPKE:后量子混合公钥加密

摘要 —公钥密码术用于以相对较高的性能成本在通信方之间非对称地建立密钥、验证或加密数据。为了减少计算开销,现代网络协议将密钥建立和验证的非对称原语与对称原语相结合。同样,混合公钥加密是一种相对较新的方案,它使用公钥密码术进行密钥派生,使用对称密钥密码术进行数据加密。在本文中,我们提出了 HPKE 的第一个抗量子实现,以解决量子计算机给非对称算法带来的问题。我们提出了仅 PQ 和 PQ 混合 HPKE 变体,并分析了它们在两种后量子密钥封装机制和各种明文大小下的性能。我们将这些变体与 RSA 和经典 HPKE 进行了比较,并表明额外的后量子开销在明文大小上摊销。我们的基于格的 KEM 的 PQ 混合变体显示 1KB 加密数据的开销为 52%,而 1MB 明文的开销降至 17%。我们报告称,基于经典、仅 PQ 和 PQ 混合 HPKE 加密 1MB 消息分别需要 1.83、1.78 和 2.15 × 10 6 个时钟周期,其中我们注意到,将量子抗性引入 HPKE 的成本相对较低。索引术语 — 后量子、混合公钥加密、后量子混合公钥加密、混合 HPKE

积少成多:可证明量子安全混合密钥交换的框架

摘要。混合认证密钥交换 (AKE) 协议结合了来自不同来源(后量子、经典和量子密钥分发 (QKD))的密钥材料,以构建能够抵御不同组件灾难性故障的协议。这些故障可能是由于量子计算的进步、实施漏洞或我们对所谓量子安全原语的量子(甚至经典)安全性的不断理解。这种混合方法是后量子安全密码原语初始部署的主要候选方法,因为它可以防范未被发现的弱点。我们提出了一个通用框架 HAKE 来分析此类混合 AKE 协议的安全性。HAKE 扩展了经典的 Bellare-Rogaway AKE 安全性模型,使其涵盖前向安全性、后妥协安全性、不同加密组件的细粒度妥协等。我们使用该框架对名为 Muckle 的新混合 AKE 协议进行安全性分析。该协议在一次往返中运行,并利用当前 QKD 设计中固有的预建立对称密钥来提供消息认证,从而避免使用昂贵的后量子签名方案。我们提供了 Muckle 协议的实现,使用经典和后量子 Diffie-Hellman 算法选择实例化我们的通用构造。最后,我们报告了针对我们实现的基准测试练习,检查了其在时钟周期、已用挂钟时间和 LAN 和 WAN 设置中的额外延迟方面的性能。

康斯坦斯改变了拟南芥的昼夜节律

植物是无柄生物,已经获得了高度塑料发育策略以适应环境。在这些过程中,口腔过渡对于确保生殖成功至关重要,并且受到多个内部和外部遗传网络的最终调节。控制植物对白天长度的响应的光周期途径是控制流动的最重要的途径之一。在ara-bidopsis光周期旋转中,constans(CO)是中心基因,它在漫长的一天结束时在叶片中激活了叶片开花基因座t(ft)的表达。昼夜节律强烈地表达了CO的表达。迄今为止,尚无关于从光周期途径回到昼夜节律的反馈回路的证据。使用转录网络,我们确定了相关的网络图案,可以调节昼夜节律之间的相互作用。基因表达,染色质免疫沉淀实验和表型分析使我们能够阐明CO在昼夜节律中的作用。植物具有改变的CO表达的植物显示出不同的内部时钟周期,通过每日叶子节奏运动来衡量。我们表明,通过与启动子上的特定位点结合,CO上调了与昼夜节律时钟相关的关键基因的表达,例如CCA1,LHY,PRR5和GI。CO上的大量PRR5抑制靶基因上调,这可以解释COCo-Prr5复合物与BZIP转录因子HY5相互作用,并有助于将复合物定位在时钟基因的启动子中。总而言之,我们的结果表明,可能有一个反馈循环,可以在其中将循环回到昼夜节律时钟,从而为昼夜节律提供了季节性信息。

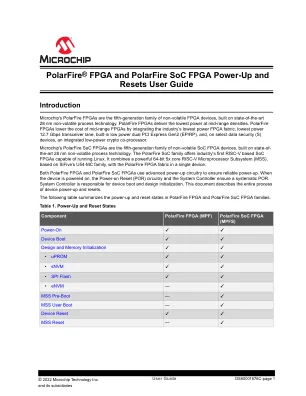

PolarFire® FPGA 和 PolarFire SoC FPGA 上电和...

注释: • 上电至功能时间基于 IO 组的 VDDI/VDDAUX 在 VDD/VDD18/VDD25 之前或之后通电的情况。IO 组启用时间从 VDD/VDD18/VDD25 的断言时间开始测量。如果 IO 组的 VDDI/VDDAUX 在 VDD/VDD18/VDD25 之后通电充足,则 IO 组启用时间从 VDDI/VDDAUX 的断言开始测量。在这种情况下,IO 操作由 BANK_#_VDDI_STATUS 的断言指示,而不是相对于 FABRIC_POR_N 否定进行测量。 • AUTOCALIB_DONE 的断言可以在 DEVICE_INIT_DONE 的断言之前或之后发生。AUTOCALIB_DONE 断言所需的时间取决于: – VDD/VDD18/VDD25 通电后 VDDI/VDDAUX 上升的时间。 – 指定用于自动校准的每个 IO 组的 VDDI 斜坡时间。 – 需要对 PCIe、SerDes 收发器和结构 LSRAM 执行多少自动初始化。 – 如果任何指定用于自动校准的 IO 组未在自动校准超时窗口内打开其 VDDI/VDDAUX,则每当 VDDI/VDDAUX 随后打开时,它都会自动校准。为了在此类 IO 组上获得准确的校准,需要启动重新校准(使用结构中的 CALIB_START)。 • 在 DEVICE_INIT_DONE 或 AUTOCALIB_DONE 断言后约 100 个系统控制器时钟周期,SUSPEND_EN 断言(如果启用了挂起模式)。 • 这两个设备系列都具有内置篡改检测功能,用于监控电压供应和标志以检测最小或最大阈值。这些标志仅在设计初始化后有效,而不是在 POR 期间有效。如果启用了系统控制器挂起模式,则必须锁存 TAMPER 标志,以便在 DEVICE_INIT_DONE 置位之后、SUSPEND_EN 置位之前,结构设计可以读取这些值。

数字定位器的新型集成诊断策略

1.定位器功能定位器最重要的任务仍然是根据过程控制系统给出的命令,尽可能快速准确地将阀门移动到所需位置。模拟定位器始终能够做到这一点,但它们不如提供自动初始化程序和大量设置的数字定位器那么方便。但由于集成微处理器的时钟周期受限,数字控制算法缺乏模拟算法的动态性。最好的方法是使用数字和模拟组件的组合进行信号处理,然后再将信号馈送到定位器的空气输出增强器。在这种定位器中,设定点 W 在进入阶段记录(图 1),这可以通过多种方式完成。在自动模式下的 4-20 mA 双线系统中,过程控制系统以 4-20 mA 信号的形式发出设定点,并由 A/D 转换器 (4) 进行数字化。在手动模式下,旋转按钮和显示屏 (16)、串行接口或叠加的 HART 信号 (FSK, 17) 可帮助将设定点转换为数字信号。在现场总线系统中,自动模式下的输入信号从一开始就始终是数字信号。内部 PD 控制器 (3) 使用数字设定点 W 和距离传感器 (2) 提供的模拟阀门行程信号 X 作为反馈来创建内部驱动信号 Y,该信号是控制 i/p 模块 (6) 和气动增压器 (7) 所必需的。增压器通过填充和排气来改变执行器中的供给压力,直到达到所需的阀门位置。另一个优点是流量调节器 (9) 的内部漏电流非常小,因为它减少了内部的影响

dpcrypto:使用GPUS上的点产生指令

摘要。DOT-PRODUCT是许多机器学习和科学计算算法中广泛使用的操作。最近,NVIDIA在现代GPU架构中引入了DOT-产品指令(DP2A和DP4A),目的是加速机器学习和科学计算应用程序。这些点 - 产品指令允许在时钟周期中计算多和添加指令,与常规的32位整数单元相比,有效地实现了更高的吞吐量。在本文中,我们表明DOT-产品指令也可以用于加速基质 - 型质子和多项式卷积操作,这些操作通常在基于量子后晶格后的密码学方案中发现。特别是我们提出了高度优化的Frodokem实现,其中矩阵 - 倍数通过点 - 产品指令加速。我们还提出了专门设计的数据结构,该结构允许使用DOT-产品指令来加速多项式卷积,从而有效地实现了Saber钥匙封装机制。拟议的Frodokem实施实现了4。每秒密钥交换操作比V100 GPU上的最先进的实施情况更高。本文还介绍了在GPU平台上的第一次实施,分别在RTX3080,V100和T4 GPU上实现了124,418、120,463和31,658密钥交换操作。由于基矩阵 - 多项式卷积操作是基于晶格的加密方案中最耗时的操作,因此我们提出的技术很可能有助于其他类似的算法。在各种GPU平台上提出的KEM的高吞吐量实现允许从服务器中填充重型计算(KEMS)。这对于许多新兴应用程序(如物联网和云计算)非常有用。

使用超低噪声 SQUID 放大器实现量子点的灵敏射频读取

半导体中的电子自旋是最先进的量子比特实现方式之一,也是利用工业工艺制造的可扩展量子计算机的潜在基础 [1–3]。一台有用的计算机必须纠正计算过程中不可避免地出现的错误,这需要很高的单次量子比特读出保真度 [4]。用于错误检测的全表面码要求在计算机的每个时钟周期内读出大约一半的物理量子比特 [5]。直到最近,自旋量子比特装置中的单次读出只能通过自旋到电荷的转换来实现,由附近的单电子晶体管 (SET) 或量子点接触 (QPC) 电荷传感器检测 [6–9]。然而,如果使用色散读出,硬件会更简单、更小,这利用了双量子点中单重态和三重态自旋态之间的电极化率差异 [10–13]。可以通过与量子点电极之一粘合的射频 (RF) 谐振器监测由此产生的两个量子比特状态之间的电容差异。量子点中的电荷跃迁也会发生类似的色散偏移,这样反射信号有助于调整到所需的电子占据 [14–16]。色散读出的优势在于它不需要单独的电荷传感器,但即使在自旋衰减时间较长的系统中,电容灵敏度通常也不足以进行单次量子比特读出 [17–23]。最近,已经在基于双量子点的系统中展示了色散单次读出 [24–28],但为了提高读出保真度,仍然需要更高的灵敏度。

硬件中的sdith-密码学EPRINT存档

摘要。这项工作介绍了综合征编码(SDITH)签名方案的第一个硬件实现,该方案是NIST PQC过程中标准化后量子安全数字签名方案的候选者。sdith的硬度基于基于保守的代码假设,它使用了多方 - 机票(MPCITH)结构。这是基于传统解码问题的基于代码的签名方案的第一个硬件设计,仅在野餐之后仅是MPCITH构造的第二个硬件。这项工作提出了优化的设计,以实现最佳的区域效率,我们使用Time-Area产品(TAP)度量进行评估。这项工作还通过将签名生成算法分为两个阶段,即OfflINE和在线阶段,以优化整体时钟周期计数,也提出了一种新颖的硬件体系结构。针对所有SDITH参数(包括NIST安全水平)的参数构成了密钥生成,签名生成和签名验证的硬塑料设计,既综合征解码基本场(GF256和GF251),因此对Sdith Speciififations进行了构象。硬件设计进一步支持秘密共享分裂,以及可以在此和其他NIST PQC候选中应用的HyperCube优化。与优化的AVX2软件实现相比,这项工作的结果导致了硬件设计,其时钟周期的大幅降低,大多数操作的范围为2-4倍。我们的密钥一代巨大的软件大大优于软件,尽管时钟速度的速度明显更快,但运行时减少了11-17倍。在Artix 7 FPGA上,我们可以在55.1 kcycles中执行关键生成,6.7 mcycles的签名生成以及nist L1参数的8.6 mcycles的签名验证,对于GF251而言增加,以及L3和L5参数。