XiaoMi-AI文件搜索系统

World File Search System使用10 nm Wrap-Gate Cntfet技术的超细胞宽带操作跨导放大器

抽象的操作跨传输放大器(OTA)是模拟电路和系统中最关键的块。随着灾难性短通道效应的互补金属氧化物半导体(CMOS)晶体管在深纳米系统下的晶体管,微电学科学家的侧重于设计基于非西硅材料的超细胞性奥塔斯。在过去的几年中,具有惊人的电气和物理性能的全面碳纳米管局部效应晶体管(GAA-CNTFET)吸引了纳米电子研究人员的广泛关注,这是代表高性能纳米级OTA的潜在平台。在这方面,这项工作旨在根据10 nm GAA-CNTFET技术节点提出一个超米型超宽带OTA。在超级尺寸的GAA-CNTFET晶体管的弹道传输操作中,提出的OTA受益,该尺寸可提供优质带宽(2.88 GHz)以及合适的功率消耗(44.8 L W)。所提出的OTA显示在1 V电源电压下的64.5 dB开环增益和59 dB的共同模式排斥比。此外,由于使用间接反馈补偿方法的利用,拟议的基于GAA-CNTFET的OTA呈现了适当的相位边缘(61),并带有较小的补偿器电容器。提到的性能指标仅占据0.198 L m 2的物理区域,提出的GAA-CNTFET OTA有可能被视为基于纳米级CMOS的OTA的替代方法。

用于量子化学的量子计算机上的资源优化的费米子局域哈密顿模拟

在量子计算机上模拟费米子系统的能力有望彻底改变化学工程、材料设计、核物理等领域。因此,优化模拟电路对于充分利用量子计算机的功能具有重要意义。在这里,我们从两个方面解决这个问题。在容错机制下,我们优化了 rz 和 t 门数以及所需的辅助量子比特数,假设使用乘积公式算法进行实现。与现有技术相比,我们获得了门数节省率为 2 和所需辅助量子比特数节省率为 11。在预容错机制下,我们优化了两量子比特门数,假设使用变分量子特征求解器 (VQE) 方法。具体到后者,我们提出了一个框架,可以使 VQE 进程向费米子系统基态能量收敛的方向引导。该框架基于微扰理论,能够将 VQE 进程每个循环的能量估计值提高约三倍,与试验台上经典可访问的水分子系统中的标准 VQE 方法相比,更接近已知基态能量。改进的能量估计反过来又会节省相应数量的量子资源,例如量子比特和量子门的数量,这些资源需要在已知基态能量的预定公差范围内。我们还探索了一套从费米子到量子比特算子的广义变换,并表明在小规模情况下,资源需求节省高达 20% 以上是可能的。

具有串联双线性的节能 delta-sigma ADC ...

Delta-sigma (ΔΣ) ADC 广泛用于信号采集和处理应用。因此,这种类型的 ADC 被用作编解码器和助听器,这些设备需要信号路径具有较大的动态范围 [1-4]。与奈奎斯特速率转换器相比,ΔΣ ADC 更易于设计,因为它们不需要具有严格参数的模拟组件。过采样转换器对输入信号带宽进行采样,因此无需使用抗混叠滤波器。通过中等过采样率和增加的采样率,可以设计高分辨率 ADC。这可以有效降低整个功耗,同时保持所需的分辨率 [5]。电压缩放适用于数字电路设计,以降低散热量,同时牺牲速度。已报道了几种解决该问题的技术,例如体驱动电路、SAR 操作、亚阈值操作 [6-9] 和过零电路 [10, 11],但这些电路的性能非常低。delta-sigma ADC 是一种非常高效的结构,具有过采样和噪声整形特性。连续 ΔΣADC 的工艺缩放因子和带宽得到了改善。高性能模拟电路包括无运算放大器流水线 ADC [12, 13]、节能逐次逼近寄存器 (SAR) ADC [14, 15] 和数字校准技术 [16, 17]。为了在时域中处理信号,压控振荡器 (VCO) 起着重要作用 [18-24]。当触发器同步时,VCO 输出会在 VCO 中引入量化误差。

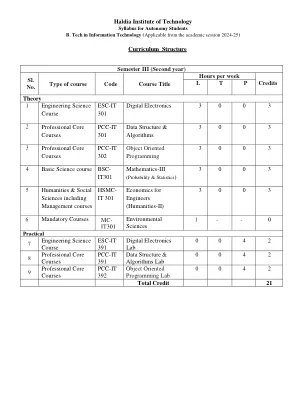

课程结构

1. IGNagrath,《模拟电子学》,PHI 2. 《模拟电子学》,AK Maini,Khanna 出版社 3. 《微电子工程》——Sedra 和 Smith-Oxford。 4. 《电子设备和电路原理》——BL Thereja 和 Sedha——S Chand 5. 《数字电子学》——Kharate——Oxford 6. 《数字电子学——逻辑和系统》,J.Bigmell 和 R.Donovan 编著;Cambridge Learning。 7. 数字逻辑和状态机设计(第 3 版)– DJComer,OUP 8. 电子设备与电路理论 – Boyelstad & Nashelsky - PHI 9. Bell-Linear IC & OP AMP—Oxford 10. P.Raja- 数字电子学- Scitech Publications 11. Morries Mano- 数字逻辑设计- PHI 12. RPJain—现代数字电子学,2/e,McGraw Hill 13. H.Taub & D.Shilling,数字集成电子学- McGraw Hill。14. D.RayChaudhuri- 数字电路-Vol-I & II,2/e- Platinum Publishers 15. Tocci,Widmer,Moss- 数字系统,9/e- Pearson 16. J.Bignell & R.Donovan- 数字电子学-5/e- Cenage Learning。 17. Leach & Malvino—数字原理与应用,第 5 版,McGraw Hill 18. Floyed & Jain- 数字基础-Pearson。课程成果:ESC 301.1 定义基本模拟电路,例如放大器、Wein 桥振荡器、多谐振荡器、Schimtt 触发器和 555 定时器。ESC 301.2 使用二进制数字系统和布尔代数的基础知识区分模拟系统和数字系统。

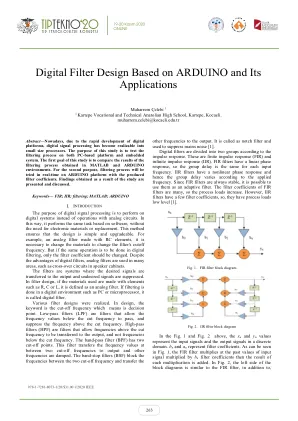

基于Arduino及其应用的数字过滤器设计

数字信号处理的目的是在数字系统上执行,而不是使用模拟电路的操作。以这种方式,它基于软件执行相同的任务,而无需电子材料或更换。此方法可确保设计简单且可升级。例如,一个用RC元素制成的模拟滤镜,有必要更改材料以更改过滤器的截止频率。但是,如果要在数字过滤中执行相同的操作,则只能更改过滤系数。尽管数字过滤器具有优势,但在许多领域(例如扬声器柜中的交叉电路)都使用了模拟过滤器。过滤器是将所需信号传输到输出的系统,并抑制了不希望的信号。在滤波器设计中,如果使用的材料是用r,c或l等元素制成的,则将其定义为模拟滤波器。如果在PC或微处理器等数字环境中进行过滤,则称为数字过滤器。实现了各种过滤器设计。在设计中,关键字是截止频率,这意味着决策点。低通滤波器(LPF)是允许低于切割频率的频率值通过的过滤器,并抑制高于切割频率的频率。高通滤波器(HPF)是允许将频率传输到输出的频率,而不是低于切割频率的频率。带通滤波器(BPF)具有两个截止点。此滤波器在两个切断频率之间传输频率值,并降低了其他频率。带挡过滤器(BSF)阻止了两个截止频率之间的频率并转移

Dylan RossesDylan Rosses

div> dylan Rosser www.dylanrosser.us工作经验高级模拟电路设计师NXP半导体NXP半导体•LED电力管理IP开发新产品介绍•与SOC Architect合作,与SOC Architect合作开发MCU电源架构和规格•建模,设计和模拟的电压参考,调节器和检测技能之间的交易•均衡•调查•调节•杠杆设计•均衡型号•衡量型号,并衡量型号,并在范围内进行衡量•均衡级别的行为•平衡巡回赛•专家•生产的可交付成果,例如示意图,网表,GD,LEF,模型,自由和文档•分析的老化,可靠性,SOA,SOA,DFMEA,可交付成果的质量模拟电路设计器II NXP半导体•模拟,优化和设计了各种用于数据转换器的iP和Power Machine IP的子计数,以实现多种机器学习的•用于机器学习的最佳FLED和DRC•DRC•DRC•DRC•DRC•DRC•DRC•drc•DREC•drc•drc•drc•drc•drc•drc•drc• IP•在SystemVerilog,Veriloga和Python中对SAR和管道ADC建模•脚本验证以自动化数据分析和可视化研究和助教Carnegie Mellon University•设计并布置了高速的两阶段比较器,在65nm CMOS中进行了高速两阶段的比较器•开发的Microelectronic Circen interne internect internement internect internement internect internection•构成了一项自动式的奖励•颁发的均等•验证电气工程师Cosentini Associates

2023 年 4 月 23 日至 26 日美国德克萨斯州圣安东尼奥 www.ieee-...

技术程序委员会 模拟电路和技术 主席:Antonio Liscidini,多伦多大学 联合主席:Edoardo Bonizzoni,帕维亚大学 委员会成员:Mark Oude Alink,特温特大学 Devrim Aksin,ADI Ping-Hsuan Hsieh,国立清华大学 Hiroki Ishikuro,庆应义塾大学 Mahdi Kashmiri,元数据转换器 主席:Seung-Tak Ryu,韩国科学技术研究院 联合主席:Lukas Kull,思科系统 委员会成员:Vanessa Chen,卡内基梅隆大学 Chia-Hung Chen,国立交通大学 Jin-Tae Kim,建国大学,韩国 Martin Kinyua,台积电 Shaolan Li,佐治亚理工学院 Qiang Li,电子科技大学 Yong Liu,博通 Zhichao Tan,浙江大学 Filip Tavernier,天主教鲁汶大学 Haiyang (Henry) Zhu,ADI 数字电路、SoC、和系统主席:Gregory Chen,英特尔公司联合主席:Saad Bin Nasir,高通委员会成员:Behnam Amelifard,高通Elnaz Ansari,谷歌Ningyuan Cao,圣母大学Jie Gu,西北大学Monodeep Kar,IBMWin-San (Vince) Khwa,台积电Bongjin Kim,加州大学圣巴巴拉分校Alicia Klinefelter,nVidiaYoonmyung Lee,成均馆大学Yingyan (Celine) Lin,佐治亚理工学院Yongpan Liu,清华大学Divya Prasad,AMDElkim Roa,格罗方德半导体Visvesh Sathe,佐治亚理工学院Shreyas Sen,普渡大学WeiWei Shan,东南大学,南京

RapidChiplet:用于快速设计空间探索chiplet体系结构的工具链

提高处理器和加速器的每成本绩效比以往任何时候都变得更具挑战性,导致摩尔定律的减慢[22]。这种慢速下降的原因是过渡到更先进的技术节点[19]时的设计和制造成本,以及由于IO驱动器,模拟电路的缩放限制以及最近的静态随机访问记忆(SRAM)而导致此过渡的重新转换。针对这些挑战的有前途的解决方案是2.5D集成,其中多个称为chiplets的硅死模被整合到同一软件包中。可以将单个芯片设计重复使用以降低每芯片的设计成本的事实。此外,由于2.5D集成允许将不同技术内置的异质芯片集成到同一包装中,因此只有可以充分利用技术扩展的组件才能以高级和昂贵的技术节点制造。达到缩放限制的组件是成熟的低成本技术制造的。由于其经济利益,2.5D整合将其进入行业领先的公司的产品,例如NVIDIA的P100 GPU [17](仅用于高频带宽度内存(HBM))和AMD的EPYC和Ryzen CPU [23]。2.5D堆叠芯片的设计空间很大。One can decide between different packaging options [ 18 , 21 , 27 , 29 ], chiplet counts and sizes [ 9 ], chiplet placements [ 13 ], die-to-die (D2D) link imple- mentations [ 7 , 24 ] and protocols [ 1 , 3 ], inter-chiplet interconnect (ICI) topologies [ 4 , 14 , 16 , 25 , 26 ], and many more factors.更重要的是,有许多感兴趣的指标,例如面积要求,功耗,热能性能以及芯片的制造成本,或ICI的潜伏期和吞吐量。

EEE 335:模拟和数字电路课程信息

EEE 335:模拟和数字电路课程信息:课程描述:模拟、数字微电子电路和系统。门尺寸、时序分析、顺序数字电路、内存。单级和差分放大器、频率响应。先决条件和要求:工程学学士/BSE 学生。必须完成 EEE 334 或同等课程,成绩为 D 或更高。课程目的:本课程是电气工程中电子和混合信号电路设计重点的区域途径课程。它是 EEE 334、电路 II 的延续。在 EEE 334 中,您将了解晶体管和电子电路的基础知识。本课程将是您的第一门真正的电子电路设计课程,重点介绍如何构建数字和模拟电路。实际设计将在配套实验室中实现,您将需要使用 CADENCE EDA 工具构建和模拟特定电路,从 CMOS 逻辑门到差分放大器。本课程最重要的特点可能是它对电子电路的时间和频域响应的处理。鉴于这一特点,强烈建议学生不仅复习他们在 EEE334 中学到的内容,还要复习 EEE 202、电路 I 中涵盖的网络分析原理。教科书:微电子电路,第 8 版。牛津大学出版社,2019 年,作者:Adel S. Sedra、Kenneth C. Smith、Tony C. Carusone 和 Vincent Gaudet。讲师:Matthew Marinella 博士,m@asu.edu。课程目标:数字和模拟 CMOS 电路和系统的分析、设计和应用。本课程将使用 CADENCE 实验室进行集成电路的模拟和设计。具体来说,本课程将涵盖以下主题。

RapidChiplet:用于快速探索 Chiplet 架构设计空间的工具链

提高处理器和加速器的性能成本比以往更具挑战性,这导致摩尔定律的减速 [22]。减速的原因在于过渡到更先进的技术节点时设计和制造成本呈指数级增长 [19],同时由于 I/O 驱动器、模拟电路以及最近的静态随机存取存储器 (SRAM) 的扩展限制,这种过渡的收益不断递减。2.5D 集成是解决这些挑战的一个有前途的解决方案,其中将多个称为小芯片的硅片集成到同一封装中。单个小芯片设计可用于多种产品,这降低了每个芯片的设计成本。此外,由于 2.5D 集成允许将采用不同技术构建的异构小芯片集成到同一封装中,因此只有能够充分利用技术扩展的组件才会采用先进且昂贵的技术节点制造。已经达到扩展极限的组件则采用成熟的低成本技术制造。由于其经济效益,2.5D 集成已应用于行业领先公司的产品中,例如 NVIDIA 的 P100 GPU [ 17 ](仅适用于高带宽内存 (HBM))和 AMD 的 EPYC 和 Ryzen CPU [23]。2.5D 堆叠芯片的设计空间巨大。人们可以在不同的封装选项[18、21、27、29]、芯片数量和尺寸[9]、芯片放置位置[13]、芯片到芯片 (D2D) 链路实现[7、24]和协议[1、3]、芯片间互连 (ICI) 拓扑[4、14、16、25、26]以及其他许多因素之间进行选择。此外,还有许多不同的相关指标,例如芯片的面积要求、功耗、热性能和制造成本,或 ICI 的延迟和吞吐量。