机构名称:

¥ 1.0

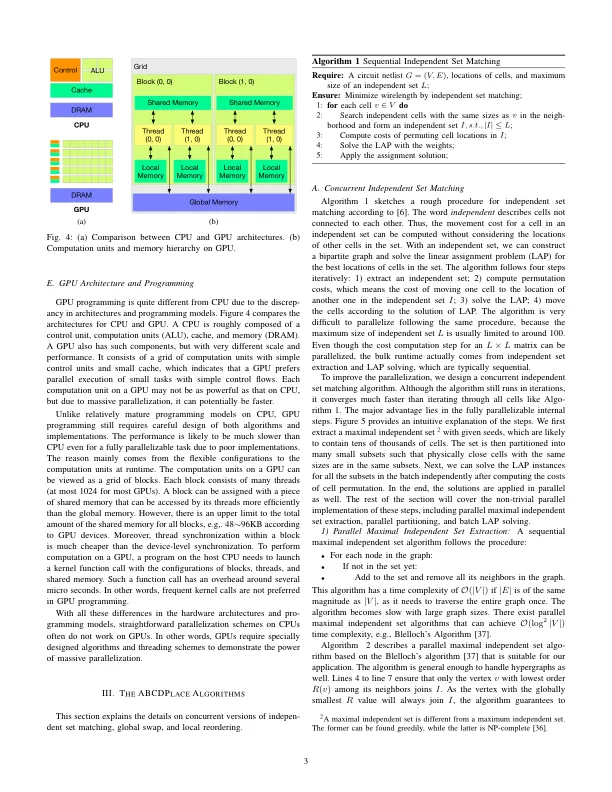

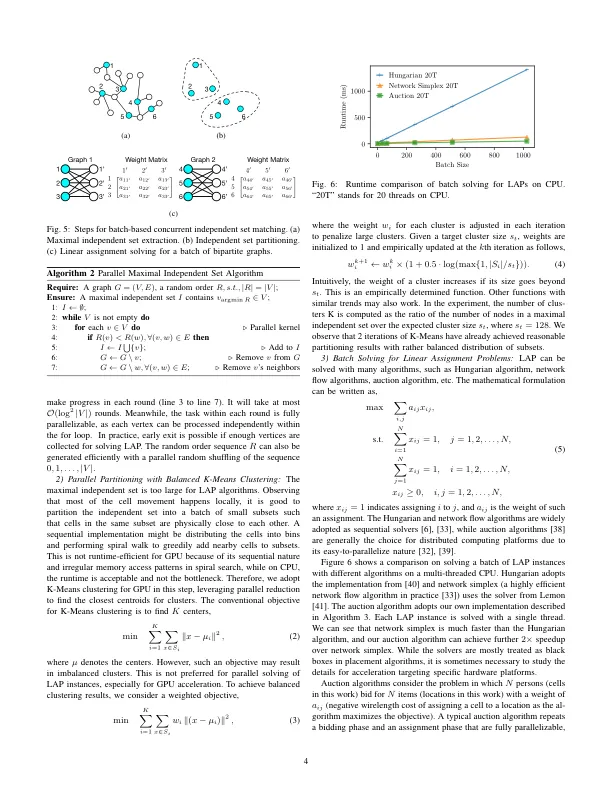

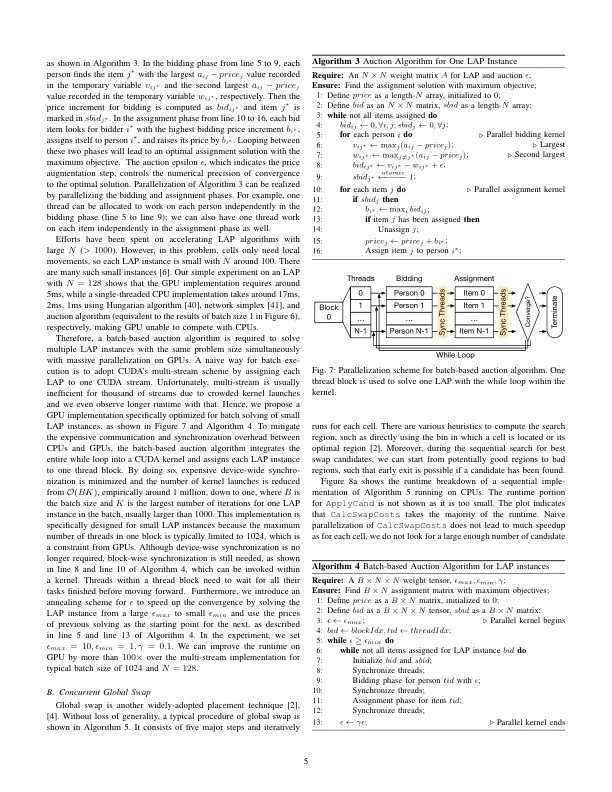

摘要 — 布局是现代超大规模集成电路 (VLSI) 设计中的重要步骤。详细布局是整个设计流程中被密集调用的布局细化程序,因此其效率对设计收敛至关重要。然而,由于大多数详细布局技术本质上是贪婪和顺序的,因此它们通常难以并行化。在这项工作中,我们提出了一个并发详细布局框架 ABCDPlace,利用多线程和 GPU 加速。我们为广泛采用的顺序详细布局技术提出了基于批处理的并发算法,例如独立集匹配、全局交换和局部重新排序。实验结果表明,在 ISPD 2005 竞赛基准上,ABCDPlace 可以比使用多线程 CPU 的顺序实现快 2 × - 5 × 的运行时间,使用 GPU 可以比顺序实现快 10 × 以上,而不会降低质量。在更大的工业基准测试中,我们展示了比最先进的顺序详细布局器快 16 倍以上的 GPU 加速。 ABCDPlace 在一分钟内完成一千万个单元的工业设计的详细布局。

ABCDPlace:在多线程 CPU 和 GPU 上加速基于批处理的并发详细布局

主要关键词