机构名称:

¥ 1.0

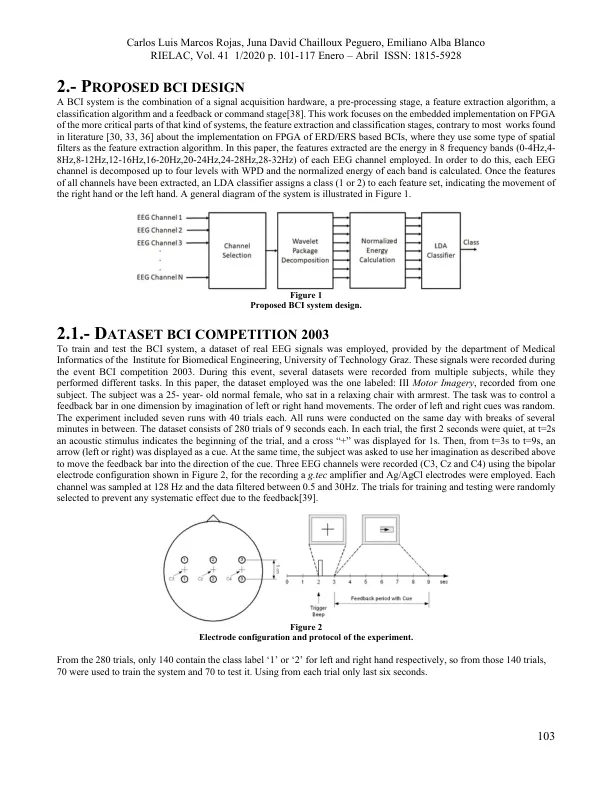

摘要 脑机接口 (BCI) 处理算法需要强大的计算设备才能实时执行。在本文中,提出了一种用于对代表两个运动想象任务的脑电图 (EEG) 信号进行分类的硬件高效设计,并在现场可编程门阵列 (FPGA) 上实现。小波包分解 (WPD) 用作特征提取算法,线性判别分析 (LDA) 用作分类器。该系统是使用 System Generator 设计的,并使用硬件/软件联合仿真在 Zybo 板上实现。仿真结果显示,在两个运动想象任务的分类过程中准确率为 80%,时钟频率为 1.5 MHz 时延迟为 7.5 毫秒,功耗为 0.102 W。此外,所使用的 FPGA 资源量少于以前的类似工作,证明设计系统不仅实现了良好的准确性,而且以高效的方式实现了这一目标。

实时识别脑电图上的运动想象动作...

主要关键词