机构名称:

¥ 1.0

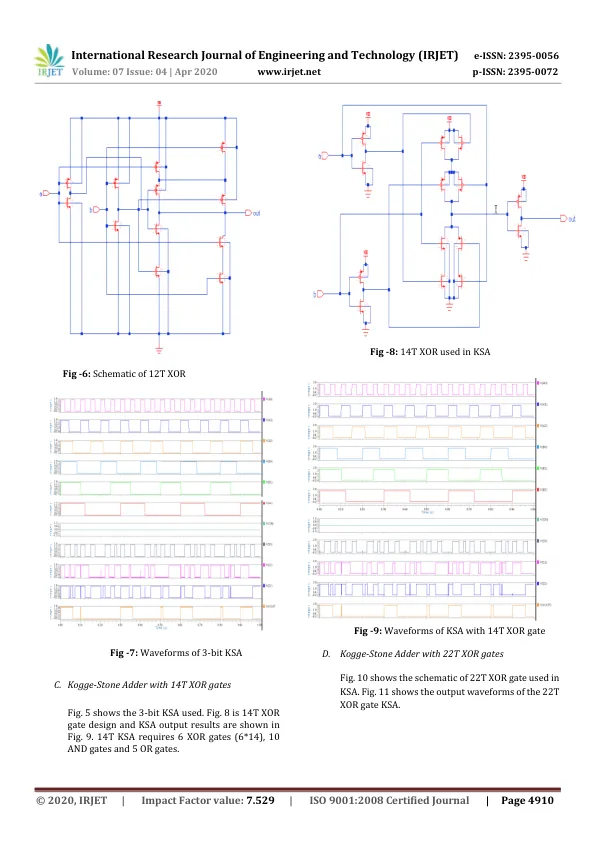

1. 引言 VLSI 技术在速度和尺寸方面的进步使得实现并行乘法器硬件成为可能。技术发展进一步确保了更好的性能特征和在 DSP 系统中的广泛使用。它执行诸如累加多个乘积之和之类的操作的速度比普通微处理器快得多。DSP 架构旨在执行并行操作,从而降低计算复杂性并提高此类应用中重复信号处理所需的速度[1]。这些功能旨在提高可编程 DSP 的速度和吞吐量。对于给定的应用,有大量可编程 DSP 可供选择,具体取决于速度、吞吐量、算术能力、精度、规模、成本和功耗等因素[2]。单芯片乘法器的引入及其与微处理器架构的结合是能够实现 DSP 功能的商用 VLSI 芯片面市的最重要原因[3]。并行前缀加法器被认为是最有效的二进制加法电路。它们的规则结构和快速性能使得它们特别适合实现 VLSI[4]。数字的乘积生成需要一个处理器周期。无论是基于软件的移位和加法算法,还是一个

采用并行前缀加法器的高速乘法器设计

主要关键词