机构名称:

¥ 1.0

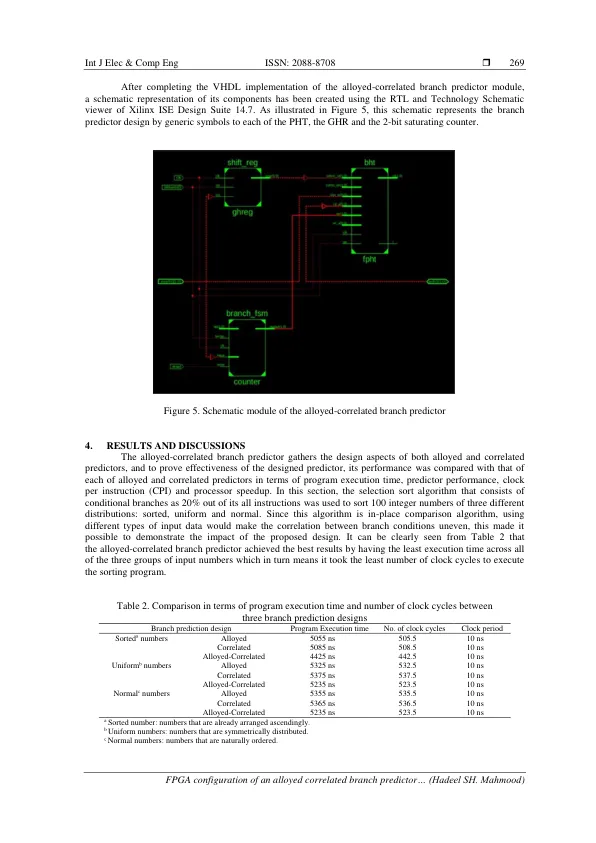

说明管道是改善处理器速度的最杰出技术之一;尽管如此,这些管道的阶段仍在不断面对由嵌套条件分支引起的摊位。在执行嵌套条件分支的过程中,跑步分支的行为取决于先前的历史记录信息;因此,这些分支在降低条件分支之间分支预测因子的预测准确性方面具有最大的影响。这项研究的目的是通过引入结合本地和全球预测技术的分支预测变量的硬件模型来减少由相关分支引起的失速周期。此预测因子将合金预测变量的预测特性与相关预测指标的预测特性相结合。在VHDL中实现的预测器设计(非常高速IC硬件说明语言)已插入先前设计的MIPS(无连锁管道管道式阶段的微处理器)中,并通过使用选择排序的算法来确认程序的预测准确性,以将不同组合的100个不同组合的输入数量分类。

FPGA配置合金相关的分支预测器

主要关键词