机构名称:

¥ 1.0

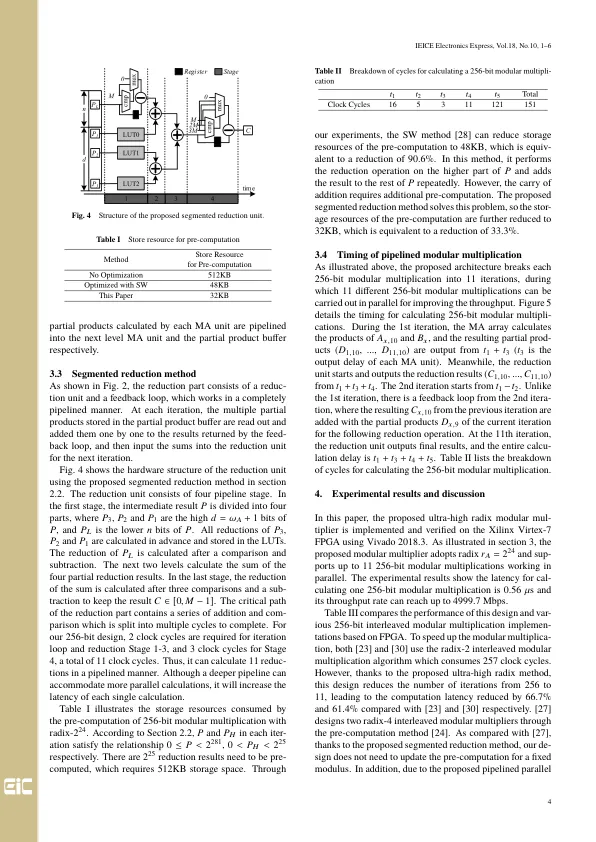

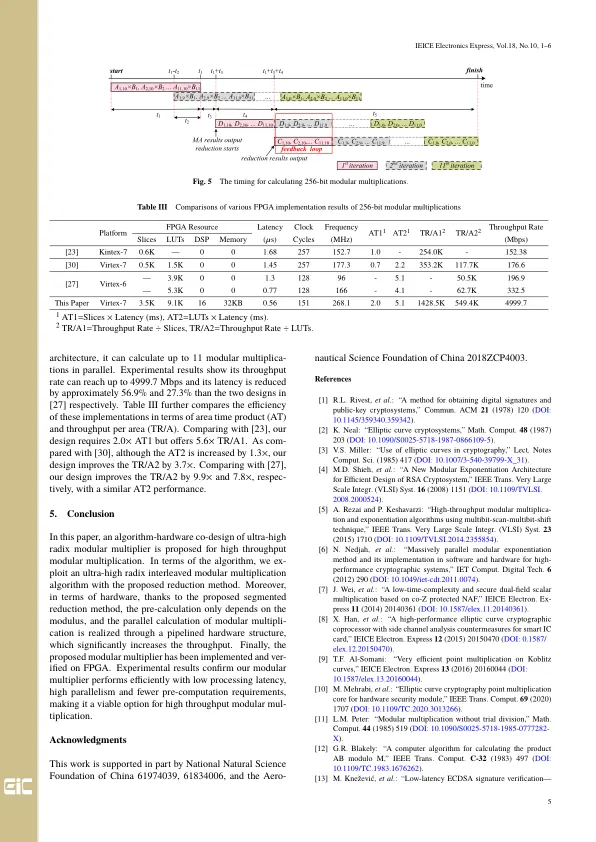

摘要本文介绍了超高辐射模块化乘数的算法 - 硬件共同设计,用于高吞吐量模块化乘法。首先,为了加快模块化乘法的速度,我们使用一种新型的分段还原方法来利用超高的radix插入模块化乘法算法,从而减少了迭代和预计的数量。然后,为了进一步改善模块化乘法的吞吐量,我们设计了高度并行的模块化乘数体系结构。最后,我们使用Xilinx virtex-7 FPGA进行了并验证模块化乘数。实验结果表明,它可以在0.56 µs中执行256位模块化乘法,吞吐量速率高达4999.7 Mbps。关键字:模块化乘法,高吞吐量,超高radix分类:集成电路(内存,逻辑,模拟,RF,传感器)

字母算法 - 硬件的超高radix基于高吞吐量模块化倍增器

![[打开]硬件的许可证](/simg/b/bc55c7314fbd77f4cab2d87e212e3f8fda676d84.webp)

![模块化 OT [手术室]](/simg/c/cd12151dc428a5ba3beb8d30a8e69c9b9a76b8bf.png)