机构名称:

¥ 1.0

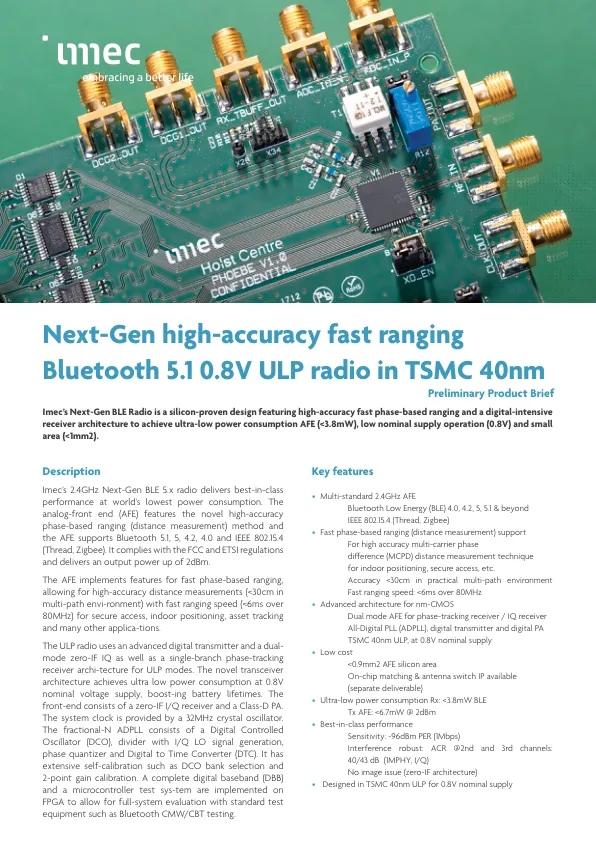

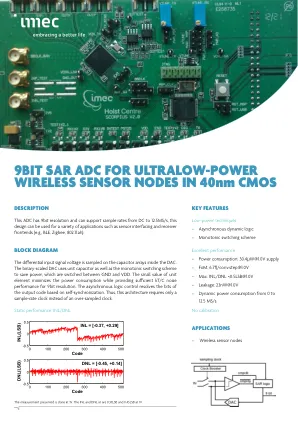

ULP无线电使用高级数字发射器和双模式零IF IQ以及ULP模式的单支相相接收器Archi-Tecture。新颖的收发器体系结构以0.8V标称电压供应,增压电池寿命实现超低功率消耗。前端由零-IF I/Q接收器和一个D级PA组成。系统时钟由32MHz晶体振荡器提供。分数-N ADPLL由数字控制振荡器(DCO),I/Q信号产生,相位量化器和数字转换器(DTC)组成。它具有广泛的自我校准,例如DCO银行选择和2点增益校准。在FPGA上实施了完整的数字基带(DBB)和微控制器测试系统,以允许使用标准测试设备(例如蓝牙CMW/CBT测试)进行全系统评估。

下一代高准确性快速远程蓝牙5.1 0.8V ULP无线电在TSMC 40nm

主要关键词