机构名称:

¥ 1.0

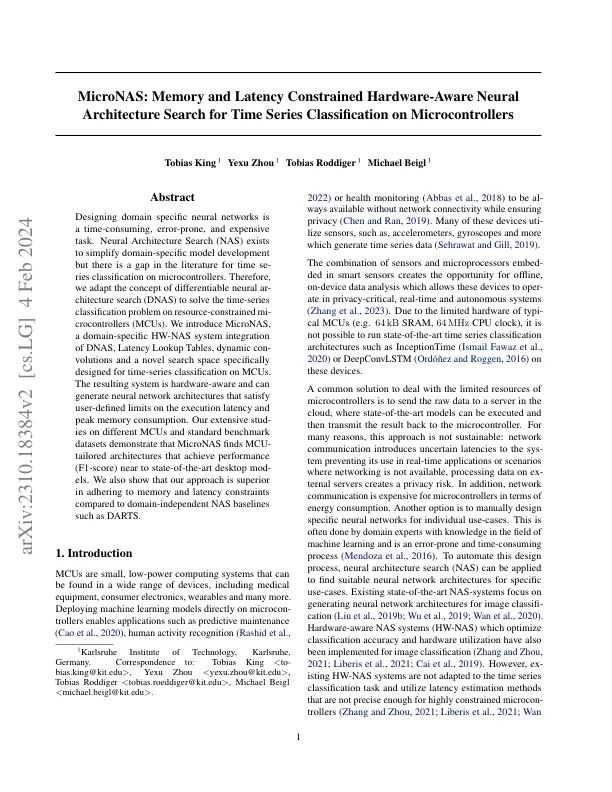

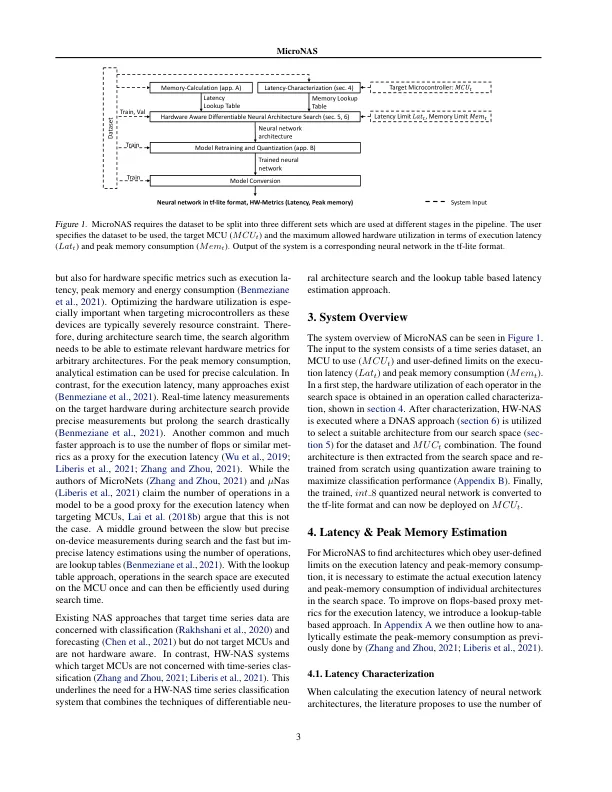

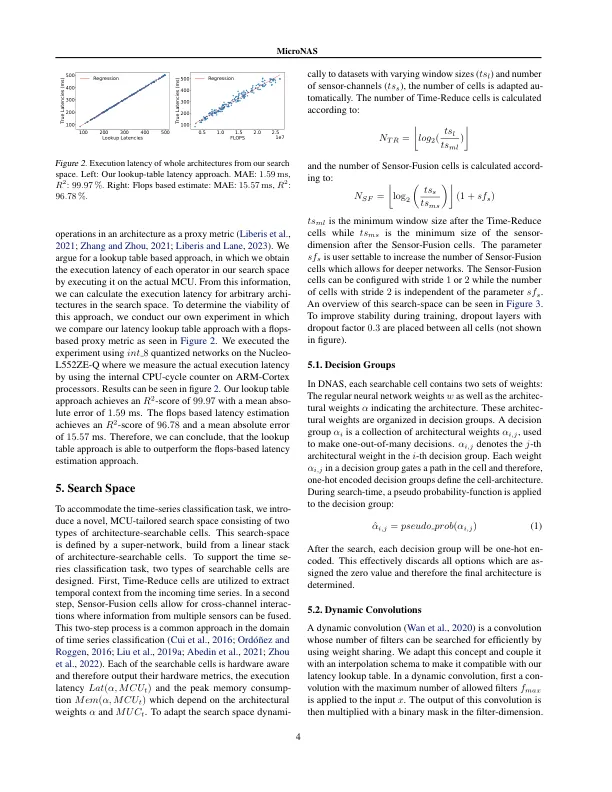

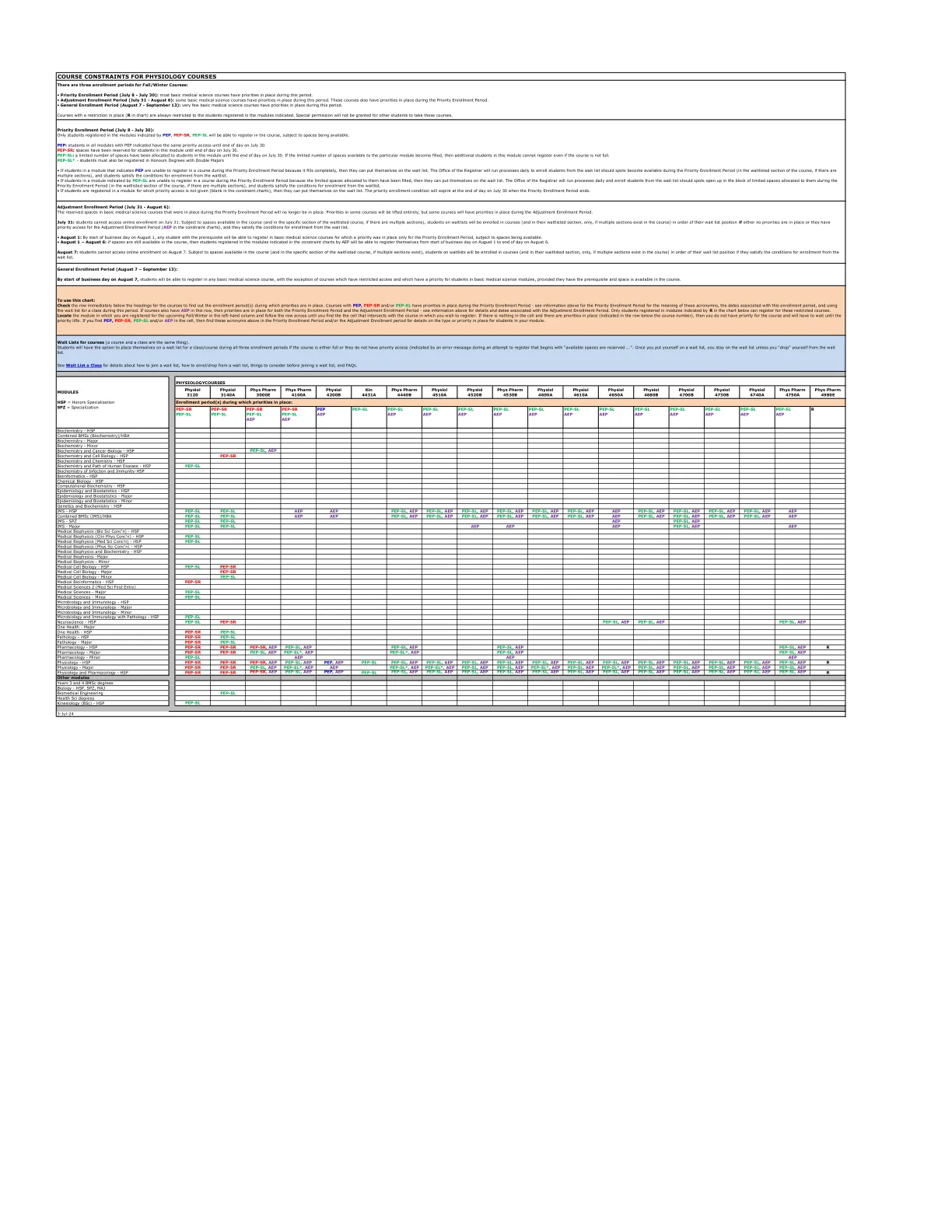

设计域特定的神经网络是一项耗时,容易出错且昂贵的任务。神经体系结构搜索(NAS),以简化特定于域的模型开发,但在微控制器上进行时间分类的文献存在差距。因此,我们调整了可区分的神经修道搜索搜索(DNA)的概念,以解决有关资源约束的Mi-Crocontrollers(MCUS)的时间序列分类问题。我们介绍了Micronas,这是DNA,延迟查找表,动态音量和专门针对MCUS时序列分类设计的新颖搜索空间的DNA,延迟查找表,动态结合表和新颖的搜索空间的Micronas。所得系统是硬件感知的,可以生成满足用户定义的执行延迟和峰值内存消耗的限制的神经网络体系结构。我们在不同的MCUS和标准基准数据集上进行的广泛研究表明,Micronas找到了达到性能的MCU量身定制的体系结构(F1得分),附近是最先进的桌面模型。我们还表明,与独立于域的NAS基准(如DARTS)相比,我们的方法在遵守记忆和潜伏期限制方面具有优越性。

micronas:内存和延迟约束硬件 -

主要关键词