XiaoMi-AI文件搜索系统

World File Search System集成系统和电路设计

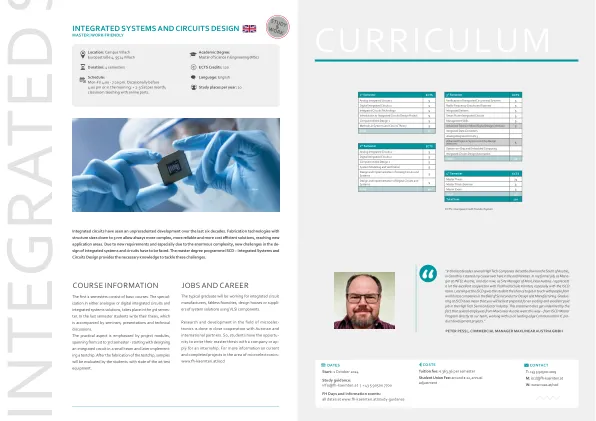

“在过去的几十年中,几家高科技公司确实在奥地利南部的卡林西亚定居。我从90年代开始就开始了我的职业生涯。在我以前的工作中,在英特尔奥地利的Manager中,现在也是奥地利Maxlinear的网站经理,我非常感谢与FachhochschuleKärnten的出色合作,尤其是与ISCD团队。在ISCD学习使学生有机会与半导体设计和制造领域的世界一流公司的人们取得联系。在ISCD毕业确实意味着您将为高科技半导体行业的一项令人兴奋且出色的有偿工作做好准备。 这一说法确实是由奥地利麦克斯林(Maxlinear)的几名员工以这种方式进行的事实 - 从ISCD主计划直接到我们的团队,与我们合作,从事领先的通信开发项目。”在ISCD毕业确实意味着您将为高科技半导体行业的一项令人兴奋且出色的有偿工作做好准备。这一说法确实是由奥地利麦克斯林(Maxlinear)的几名员工以这种方式进行的事实 - 从ISCD主计划直接到我们的团队,与我们合作,从事领先的通信开发项目。”

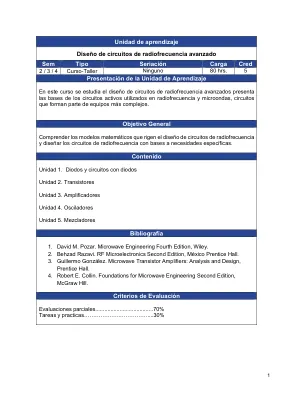

射频电路设计

由于大量射频 (RF) 和微波 (MW) 应用,高频电路设计领域正受到工业界的广泛关注。改进的半导体器件使得高速数字和模拟系统得以广泛应用,如无线通信、全球定位、雷达以及相关的电气和计算机工程学科。这种兴趣转化为对具有全面高频电路设计原理知识的工程师的强烈需求。然而,对于学生、专业工程师甚至教授这门课程的教师来说,存在一个普遍的问题。现有的大多数教科书似乎针对两类不同的受众:A) 具有广泛理论背景的高级研究生水平人群,和 B) 对数学和物理严谨性不感兴趣的技术人员。因此,RF 电路设计以两种截然不同的形式呈现。对于高级学生来说,进入该领域通常是通过电磁场方法,而对于技术人员来说,嵌入在基尔霍夫定律中的基本电路方面是首选方法。这两种方法都很难充分解决高频设计原理的理论和实际问题。基本电路方法缺乏或只是表面上涵盖了电流和电压的波动性质,而电流和电压的反射和传输特性是射频电路行为不可或缺的要素。电磁场方法当然涵盖了波导和传输线方面,但远远没有触及设计高频放大器、振荡器和混频器电路的重要方面。这本教科书的目标是以一种方式开发射频电路设计方面,以便在不采用电磁场方法的情况下明确传输线原理的必要性。因此,除了大多数学院和大学提供的场和波一年级本科物理课程外,不需要任何电磁背景。具备基本电路理论知识和/或微电子学知识的学生可以使用本书,并涵盖从传输和微带线的基本原理到各种高频电路设计程序的整个范围。冗长的数学推导要么被放到附录中,要么放在与正文分开的例子中。这样可以省略一些枯燥的理论细节,从而将重点放在主要概念上。为了接受提供高水平设计体验的挑战,我们提供了许多例子,这些例子详细讨论了各种设计方法的哲学和复杂性,在许多情况下,这些例子长达数页。

高级半径电路设计

1。David M. Pozar。 微波工程第四版,威利。 2。 Behzad Razavi。 RF微电子第二版,墨西哥Prentice Hall。 3。 GuillermoGonzález。 微波晶体管放大器:分析和设计,Prentice Hall。 4。 罗伯特·E·柯林(Robert E. Collin)。 Microwave Engineering第二版的基础,McGraw Hill。David M. Pozar。微波工程第四版,威利。2。Behzad Razavi。RF微电子第二版,墨西哥Prentice Hall。3。GuillermoGonzález。微波晶体管放大器:分析和设计,Prentice Hall。4。罗伯特·E·柯林(Robert E. Collin)。Microwave Engineering第二版的基础,McGraw Hill。

可扩展快速光路交换的电路设计

2.1 (a) 垂直 MEMS 耦合器的 (a) 关闭状态和 (b) 开启状态示意图 - 图片取自 [14] (c) MEMS 开关单元的 SEM - 图片取自 [22] . . 7 2.2 MEMS 开关元件的代表性传递函数。 . . . . . . . . . . . . . 8 2.3 (a) 128x128 SiPh MEMS 纵横开关 (b) 4x4 CMOS 高压驱动芯片倒装芯片接合到 SiPh MEMS 芯片的 GDS 屏幕截图。 . . . . . . . . . . . . 9 2.4 (a) SuperSwitch 1 高压驱动芯片的显微照片 (b) 驱动芯片的卡通布局图。 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 2.5 假设采用单个 CMOS 芯片,则激活 128 行中的 1 行的简单原理图。 . 11 2.6 假设采用 4x4 CMOS 芯片阵列,则控制 128x128 开关的原理图。 12 2.7 (a) N c = 1 时第 0 列和第 1 列的逻辑 (b) N c = 2 时第 0 列和第 1 列的逻辑。 13 2.8 (a) 带有用于调试的环回多路复用器的 SuperSwitch1 控制芯片扫描架构的最终原理图。 (b) SuperSwitch1 控制器芯片的最终参数。 . . . . . 14 2.9 (a) SuperSwitch1 高压驱动电路原理图。 (b) 所有电源及其标称值的列表。 . . . . . . ... 19 2.13 (a) HVDD = 70 V、HVSS = 65 V 时所有角的 VSS 电阻 shmoo 图。 (b) 相同图,但 HVDD = 70 V、HVSS = 66 V。 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 2.16 (a) 凸块 CMOS 焊盘的显微照片。(b) Au UBM 和 Au 微凸块的横截面。(c) 使用不同厚度的 UBM 在 SiPh 芯片上补偿 CMOS 焊盘高度差异的键合工艺说明。. . . . . . . . . 22

团问题的电路设计及其在...上的实现

在图中查找团伙因其模式匹配能力而有多种应用。k -团伙问题是团伙问题的一种特例,它确定任意图是否包含大小为 k 的团伙,该问题已在量子领域得到解决。列出所有大小为 k 的团伙的 k -团伙问题变体在现代也有流行的应用。尽管如此,这种 k -团伙问题变体在量子环境中的实现仍未触及。在本文中,除了此类 k -团伙问题的理论解决方案之外,还使用 Grover 算法解决了基于量子门的实际实现。该方法进一步扩展到设计经典-量子混合架构中最大团伙问题的电路。该算法自动为任何给定的无向无加权图和任何给定的 k 生成电路,这使我们的方法具有广义性。与最先进的方法相比,对于大图的小 k ,提出的解决 k -团伙问题的方法表现出量子比特成本和电路深度的降低。还提出了一个可以将团问题自动生成电路映射到量子设备的框架。使用IBM的Qiskit对实验结果进行了分析。

ELEC4604 射频电子电路设计

课程召集人:R. Ramer 教授,308 室,ror@unsw.edu.au 导师:如上所述 实验室联系人:Yunhao Fu,320 室,Yunhao.Fu@student.unsw.edu.au Sheng Huang,320 室,Sheng.Huang@unsw.edu.au 咨询:我们鼓励您在课程时间结束后就课程材料提问,而不是通过电子邮件提问。讲师咨询时间将在讲座期间告知。欢迎您给导师或实验室演示者发送电子邮件,他们可以回答您关于本课程的问题,也可以为您提供咨询时间。所有电子邮件咨询都应从您的学生电子邮件地址发送,主题行中注明 ELEC 4604;否则,将不会得到答复。讲师咨询时间:星期三,EE&T TBA。保持知情:通知可能会在课堂上、通过电子邮件(发送至您的学生电子邮件地址)和/或通过在线学习和教学平台发布 - 在本课程中,我们将使用 Moodle https://moodle.telt.unsw.edu.au/login/index.php 。请注意,您将被视为已收到此信息,因此您应仔细记下所有通知。

集成电路设计与技术(ICICDT)

范围和主题 我们诚征原创论文,介绍与半导体电路、设计、器件、技术和工艺相关的设计技术边界,包括但不限于以下领域:• 先进材料和加工技术• 功率半导体技术和电路• 先进封装、横向和垂直(2.5D 和 3D)集成• 复合半导体、2D 材料• 数字电路、低功耗存储器件和电路• RF/模拟、混合信号、ESD 保护器件和电路• 制造、产量和测试设计• 片上系统 (SoC) 和系统级封装 (SiP) 设计集成• 新兴技术、电路和应用(MEMS、存储器、物联网、自动驾驶汽车、机器学习、人工智能)

集成电路设计和 FPGA 应用

Florin Udrea 是剑桥大学半导体工程教授兼高压微电子和传感器实验室负责人。Udrea 教授在期刊和国际会议上发表了 550 多篇论文。他在功率半导体器件和传感器领域拥有 150 多项专利(独特的发明)。Florin Udrea 教授于 2011 年至 2019 年期间担任剑桥企业董事会董事。由于他“对英国工程的杰出个人贡献”,他被授予皇家工程院银质奖章。2015 年,Florin Udrea 教授当选为皇家工程院院士。2018 年,Udrea 教授获得了多项重要奖项,包括皇家学会颁发的著名 Mullard 奖章。2021 年,Udrea 教授被《商业周刊》评为“年度学术企业家”。