XiaoMi-AI文件搜索系统

World File Search System“ AI会创造宗教吗?”

摘要。无人机在私人和专业环境中变得普遍。人类无人机协作的工程提出了独特的挑战。特定的是,无人机的独特功能产生了巨大的设计空间。然而,相关的指导散布在文献中,因此缺少各种设计维度的概述。本文综合了足够的研究,并以形态框(MB)的形式概述了基本的设计维度,以支持无人机设计人员的紧急情况。使用此MB,实践者和研究人员意识到在设计无人机和人类之间的无人机或协作时必须做出的设计决策。它防止了无人机设计上的分散或部分视角,并为结构化的整体设计探索提供了基础。使用无人机情况,我们讨论了设计科学研究(DSR)的形态分析的潜力。新型的社会技术系统涉及庞大的多维设计空间,而单数研究经常涉及该空间的域或纪律特定小节。我们声称形态分析支持跨学科边界的设计空间的系统利用,并可能有助于对DSR工件的更透明,更可追溯的设计。

探索使用触摸式飞行控制面板为飞行员提供飞行控制...

触摸技术有望取代客机驾驶舱中现有的飞行员系统界面。使用触摸屏为飞行员和制造商提供了许多优势。然而,它也给航空安全带来了重大潜在风险。在本文中,我们探索了未来飞行员触摸式飞行控制面板的设计空间。我们尝试设计在不稳定条件下更具物理性和鲁棒性的手势,并且需要更少的视觉焦点,这些手势基于利用空间和本体感受技能的方向性手势和布局。我们观察了在湍流条件下实际飞行过程中控制面板的使用情况。这让我们探索了触摸式交互技术在使用环境恶化的情况下的局限性,并探索了有形和具体交互中的有形属性如何帮助设计这些手势。这也让我们更好地理解了触摸式交互和有形交互之间模糊的边界,并通过迭代构建明确的设计空间来反思退化环境中的交互设计原则。© 2019 作者。由 Elsevier B.V. 出版。同行评审由第 8 届国际航空运输会议 – INAIR 2019、全球航空趋势科学委员会负责 关键词:触摸式交互;基于手势的交互;有形交互;有形交互设计方法;有形框架;退化环境;航空学

应用于云资源分配问题的异构系统设计空间探索

摘要。云计算服务提供商为应用程序提供按需计算资源。寻找适合用户预算、满足应用程序性能和约束的最佳云资源分配仍然是一项研究挑战。云资源分配问题与设计空间探索 (DSE) 问题非常相似,因为它们都必须在充足的设计空间中找到合适的硬件配置,而它们的目标不相容,并受到多种约束。这项工作通过应用设计空间探索技术提出了一种解决云资源分配问题的方法。我们从 DSE 工具 MultiExplorer 设计并开发了一个软件扩展 MultiExplorer-VM,该工具具有根据用户需求和应用程序约束提供虚拟机配置的工作流程。已经进行了一系列全面的实验来评估和验证所提出的工具。我们还将我们提案中的解决方案与其他现有的研究工作进行了比较,这些研究工作侧重于基于 Paramount 交互 (PI) 技术的云资源分配问题。结果表明,MultiExplorer-VM 比 PI 技术取得了显著 (更好) 的结果。 MultiExplorer-VM 带来的成本结果与 PI 技术相比降低了 8.8 倍。实验还表明,对于大多数应用程序,MultiExplorer-VM 实现了最佳云配置。

利用资源估算来开发量子计算应用程序

摘要 — 近年来,量子计算在软件和硬件方面都取得了长足的进步。但要释放量子计算机解决无法有效解决的问题的能力,大规模量子计算必不可少。不幸的是,量子模拟器的复杂性呈指数级增长,同时,目前可用的量子计算硬件仍然相当有限(即使路线图做出了有趣的承诺)。因此,为了评估量子计算应用,最终用户仍然经常被限制在玩具大小的问题实例中(此外,这些实例通常不考虑纠错)。这极大地阻碍了现实世界量子计算应用的开发和评估。在这项工作中,我们展示了如何利用资源估计来改善这种情况。我们展示了如何用估算步骤来补充当前的工作流程(依赖于模拟和/或执行),从而使最终用户 (1) 实际上可以考虑当今现实世界的问题实例(同时考虑错误更正方案和相应所需的硬件资源),(2) 可以开始探索整个设计空间中这些实例的可能优化,以及 (3) 可以结合硬件开发趋势的假设来得出更明智、更好的设计空间参数。总的来说,这使得最终用户今天就可以查看未来可能的量子计算应用的前景,即使执行它们的相应硬件尚未可用。

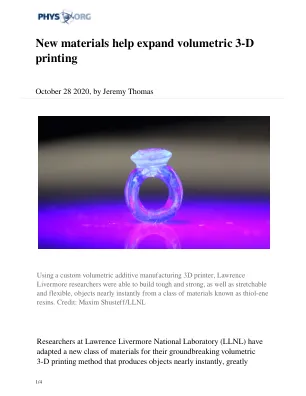

新材料助力扩大体积3D打印

此前,研究人员使用丙烯酸树脂,通过 CAL 工艺生产出易碎易碎的物体。然而,通过精心平衡三种不同类型的分子而产生的新树脂化学性质更加灵活,为研究人员提供了灵活的设计空间和更广泛的机械性能。利用硫醇-烯树脂,研究人员能够使用 LLNL 的定制 VAM 打印机制造出坚韧、坚固、可拉伸且柔韧的物体。这项研究最近发表在《先进材料》杂志上,并在《自然》杂志上重点报道。

arXiv:2305.03243v1 [quant-ph] 2023 年 5 月 5 日

近年来,嘈杂中型量子计算 (NISQ) 占据了新闻头条,而容错量子计算 (FTQC) 的长期愿景则具有巨大的潜力,尽管目前资源成本和量子纠错 (QEC) 开销难以解决。对于感兴趣的问题,FTQC 将需要数百万个具有长相干时间、高保真度门和紧凑尺寸的物理量子位,才能超越经典系统。正如异构专业化在经典计算中提供了扩展优势一样,它同样在 FTQC 中引起了人们的兴趣。然而,由于设计空间巨大和物理约束多变,在 FTQC 系统的硬件或软件元素中系统地使用异构性仍然是一个严峻的挑战。本文通过介绍用于设计异构量子系统的工具箱 HetArch 并使用它来探索异构设计场景,应对了使异构 FTQC 设计实用化的挑战。我们使用分层方法,将量子算法依次分解为更小的操作(类似于经典应用内核),从而大大简化了设计空间和由此产生的权衡。我们专门针对超导系统,设计由各种超导设备组成的优化异构硬件,将物理约束抽象为设计规则,使设备能够组装成针对特定操作进行优化的标准单元。最后,我们提供了一个异构设计空间探索框架,将模拟负担减少了 10 4 倍或更多

创建基于人工智能的游戏玩法的设计注意事项

人工智能已应用于游戏设计和开发过程的许多方面。尽管这已导致游戏和人工智能研究取得了许多进步,但仍有一些游戏以参与人工智能过程为中心:基于人工智能的游戏的设计空间仍未得到充分探索。通过从不同角度研究广泛的游戏体验,可以确定,以人工智能为先导的游戏对玩家、设计师以及游戏学术领域本身都有益。此外,有证据表明,符号方法(而非统计方法)有助于获得具有更多主动性、更强的人类可解释性和更可控制的可创作性的体验。

回顾:Aladdin:一款预 RTL、高性能加速器模拟器,支持定制架构的大型设计空间探索

Aladdin [1] 是一个预 RTL 功耗/性能模拟器,旨在实现以加速器为中心的系统的快速设计空间搜索。该框架将算法的高级语言描述作为输入(C 或 C++),并使用动态数据依赖图 (DDDG) 作为加速器的表示,而无需生成 RTL。从无约束程序 DDDG(对应于加速器硬件的初始表示)开始,Aladdin 对图形应用优化和约束,以创建加速器活动的真实模型。我们针对一系列应用,通过手写 Verilog 和商用高级综合 (HLS) 工具对加速器的 RTL 实现验证了 Aladdin。我们的结果表明,与传统 RTL 流程生成的加速器设计相比,Aladdin 可以高精度地模拟功耗、性能和面积,误差在 10% 以内,同时以更少的设计工作量和时间提供这些估算。 Aladdin 可以捕捉加速器设计的权衡,从而为异构系统(包括加速器、通用核心和共享内存层次结构,例如在移动 SoC 中看到的)提供新的架构研究方向。特别是,Aladdin 允许用户在异构环境中探索加速器的定制和共享内存层次结构。例如,在使用 GEMM 基准的案例研究中,Aladdin 通过评估整个系统的更广泛设计空间发现了重要的高级设计权衡。我们设想 Aladdin 既可以用作加速器模拟器,也可以用作未来多加速器系统的设计空间探索工具。

受约束和开放的神经生理激活...

设计空间的概念起源于问题空间的形成,并且在过去60年中一直是调查和辩论的主题。在信息处理理论的问题空间理论(Newell&Simon,1972)中,基于一般问题解决方案计算机程序(1957年),新约束,子目标和设计替代方案从问题空间中引起的新约束,子目标和设计替代方案会导致外部记忆表现形式的转变,例如模型和图纸,例如,会考虑到问题的变化。问题解决者检索系统,无论是人类还是计算能力系统,都会在搜索解决方案时不断修改和表征问题空间。那时,人们认为井和不确定的问题(Reitman 1964)或结构性不佳的问题(Newell 1969)被认为取决于问题解决者可用的问题解决方法和技术。对问题解决者容量的这种依赖性源于这样的观念,即没有结构性的问题,仅在有限的能力的范围内为解决问题的人(Simon 1973)正式形式化了结构性的问题,并且根据问题的目标,约束和生成的替代方案。一种认知设计理论的替代方法,后来成为反思实践(Schön1983; 1987)。在这种方法中,设计师通过思考和做事,因此知道行动(Argyris等人)(1985),将构建设计世界,并设定问题空间的维度以及他/她试图找到解决方案的举动(Schön,1992)。所处的认知研究方法(Clancey 1997)随后出现了许多与社会科学,行为和动态神经过程有关的学科和目标,以了解知识和行动的观点,并支持学习的想法,即学习发生在做某事时。所在的一词强调,感知机制因果关系将人类认知与环境和行动联系起来。位置涉及内部组织以及内部和外部组织之间发生的因果关系,改变了世界上的事物。新的观察方式和改变世界的改变方式随着时间的流逝而发展。作为一种研究方法,出现了适当的认知披露,以研究设计中的人类认知(Gero 1990)。设计是一种时间和多模式的活动,要求对位置的请求提供适当的解决方案,当这些请求打开时,请在解决问题的阶段发生在解决问题的阶段之前,要求发现问题和问题框架(Runco 1994; Runco和Nemiro,1994)。在过去的40年中,出现了解决问题的空间的替代视图,重点关注变化的最终目的,即解决方案空间。1.1设计空间在理解设计方面的一个有用的抽象是设计空间的概念,设计师探索了可能性的抽象空间(Amstel等人。2016; MacLean等。这两种观点都基于诸如协议分析等方法的设计认知研究(Goldschmidt,2014; Kan&Gero,2017)。虽然受约束的设计空间通常受到特定要求的限制,但开放的设计空间扩展2011)在问题空间内的探索开始,设计过程的问题解决观点(Goel&Pirolli,1992; Goel,1994; Goolschmidt,1997),而其他人则声称设计是通过产生解决方案空间的(Dorst,2019; Dorst&Cross 2001; Dorst&Cross 2001; Gero&Gero&cross&cross&verer&krer&krer&kumar; krer&kumar&kumar&kumar; 2009年;吉川,1981年)。另一种观点是,根据设计请求的限制水平和对创意探索的开放程度,设计空间可以受到限制或开放,这是本文报告的研究重点。

![arXiv:2305.03243v1 [quant-ph] 2023 年 5 月 5 日](/simg/9\986bd571bae182b86d69ddff468792177c1a6874.webp)