XiaoMi-AI文件搜索系统

World File Search System对CMOS数字电路的泄漏减少技术的调查纳米级制度

摘要电池驱动的便携式系统是现代时代的生命线。非常大规模的集成(VLSI)设计师一直在努力提高便携式系统的性能。小尺寸,快速响应和高电池备份是便携式系统的主要因素。将金属氧化物半导体场效应晶体管(MOSFET)尺寸缩放为设计低尺寸系统。必须在每个新技术节点上缩放电源和阈值电压,以保持设备的性能。缩放设备阈值电压会产生泄漏电流。泄漏电流的量在集成水平上很大,并且会损害系统的特性。因此,需要泄漏电流缓解措施,尤其是在较低技术节点,以增加便携式系统的电池备份。减少泄漏技术的数量在不同的抽象水平下可用。在本评论论文中,使用不同现有电路泄漏技术的目标探索了低功率VLSI场的系统流。nand3门通过使用不同的现有泄漏技术来进行比较目的设计和模拟在16 nm技术节点上。

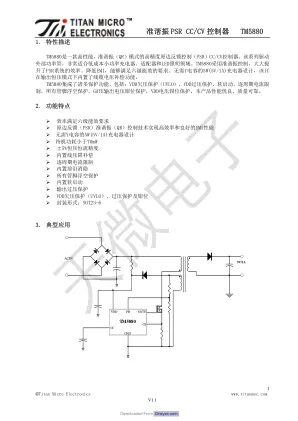

准谐振PSR CC/CV 控制器TM5880

VDD欠压保护 UVLO(OFF) VDD 电压下降 8.5 9.5 10.5 V VDD启动电压 UVLO(ON) VDD 电压上升 14 15.5 16.5 V VDD过压保护 VDD_OVP 31 33 35 V VDD钳位电压 VDD_Clamp I(VDD)=7mA 33 35 37 V 反馈输入部分(FB管脚) 反馈参考电压 VFB_EA_Ref 1.98 2.0 2.02 V 输出过压保护阈值电压 VFB_OVP 2.4 V 输出短路阈值 VFB_Short 0.65 V 输出短路钳位频率 FClamp_Short 40 KHz 退磁比较器阈值 VFB_DEM 75 mV 最小关断时间 Tmin_OFF 2 uSec 最大关断时间 Tmax_OFF 3 mSec 最大线缆补偿电流 ICable_max 40 uA 电流检测部分(CS管脚) CS前沿消隐时间 T-blanking 500 nSec 芯片关断延迟 TD_OC CL=1nF at GATE 100 nSec 恒流控制部分(CC管脚) 内部CC基准电压 V_CC_ref 490 500 510 mV

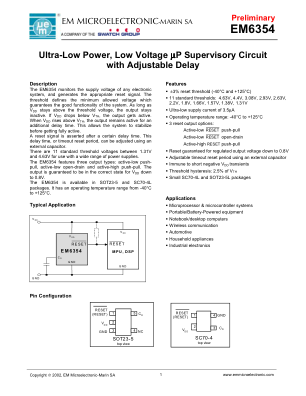

EM6354

描述 EM6354 监控任何电子系统的电源电压,并生成适当的复位信号。阈值定义了允许的最小电压,可保证系统正常运行。只要 V DD 保持在阈值电压以上,输出就保持非活动状态。如果 V DD 降至 V TH 以下,输出将变为活动状态。当 V DD 升至 V TH 以上时,输出将在一段额外的延迟时间内保持活动状态。这可使系统在完全活动之前稳定下来。在一定延迟时间后发出复位信号。可以使用外部电容器调整此延迟时间或超时复位时间。有 11 个标准阈值电压介于 1.31V 和 4.63V 之间,可与各种电源一起使用。EM6354 具有三种输出类型:低电平有效推挽、低电平有效开漏和高电平有效推挽。当 V DD 低至 0.8V 时,输出保证处于正确状态。 EM6354 采用 SOT23-5 和 SC70-4L 封装。其工作温度范围为 -40°C 至 +125°C。

商用 1.2 kV 4H-SiC 功率 MOSFET 栅极漏电流行为调查

摘要 — 过去十年,碳化硅 (SiC) 功率金属氧化物半导体场效应晶体管 (MOSFET) 的商业化不断扩大。栅极氧化物可靠性是 SiC 功率 MOSFET 的主要问题,因为它决定了器件的使用寿命。在这项工作中,我们研究了商用 1.2 kV SiC 功率 MOSFET 在不同栅极电压下的栅极漏电流。高氧化物电场引发的碰撞电离和/或阳极空穴注入 (AHI) 导致空穴捕获,从而增强了栅极漏电流并降低了器件的阈值电压。由于 Fowler-Nordheim (FN) 隧穿而产生的电子注入和捕获往往会降低栅极漏电流并增加阈值电压。还对商用 MOSFET 进行了恒压时间相关电介质击穿 (TDDB) 测量。栅极漏电流的结果表明,场加速因子的变化是由于高栅极氧化物场下栅极电流/空穴捕获增强所致。因此,建议在低栅极电压下进行 TDDB 测量,以避免在正常工作栅极电压下高估寿命。

设计注意事项

对于P通道MOSFET,vinVg + v th其中,v g = gate-wtwoltage v th =阈值电压v out =输出电压v in =输入电压以打开N通道设备,栅极量必须大于输出电压。这将需要额外的偏置电源,以使栅极电压高于输出电压。与此相比,对于P通道设备,最小输入电压必须大于P通道晶体管的阈值电压(通常是这种情况)。从中,P通道MOSFET比N通道MOSFET的优势显而易见。ON/OFF控制器或门驱动器电路更简单。对于低压驱动应用,N通道高侧开关的栅极驱动器需要一个引导电路,该电路在电动机电压轨或隔离电源上方创建栅极电压以将其打开。更大的设计复杂性导致设计工作增加和更大的空间利用。与负载开关应用程序类似,使用P通道MOSFET可以在此处减少资源的使用。ir Hirel具有最大的RAD硬P通道MOSFET的投资组合,具有不同的包装选项,并且在辐射环境中具有高性能。

设计和实施低功耗...

移动,电池电力系统(例如蜂窝电话,个人数字助手等)不断增长的市场要求设计具有低功率耗散的微电子电路。更一般而言,随着芯片的密度,大小和复杂性继续增加,提供足够冷却的困难可能会增加大量成本,或者限制使用这些集成电路的计算系统的功能。在过去十年中,已经提出了几种设计低功率电路的技术,方法和工具。但是,其中只有少数在当前设计流中找到了自己的方式[1]。在CMOS电路中,有三个主要的功率耗散来源。这些是开关功率,短路电源和泄漏功率。开关功率是由于电路驱动的充电和排放电容器。短路功率是由同时进行PMOS/NMOS晶体管对时产生的短路电流引起的。最后,泄漏功率起源于底物注入和子阈值效应。导致泄漏功率增加的主要原因之一是子阈值泄漏功率的增加。当技术尺寸缩小时,电源电压和阈值电压也会缩小。子阈值泄漏功率随着阈值电压的降低而成倍增加。堆栈方法,强制NMO,强制PMO和困倦的门将方法是一些泄漏电流减少方法[2]。

首先在1.2 kV SIC MOSFET身体二极管鲁棒性测试

1。上下文SIC MOSFET由于其强劲的损失而广泛用于新应用设计,并且具有高开关频率和高工作温度的功能。与氧化门相关的可靠性问题已经很好地解决,并且已经发表了许多有关阈值电压不稳定性的研究[1; 2]。使用车身二极管避免外部Schottky二极管[3; 4]。在本研究中,对1.2 kV的SIC MOSFET体二极管进行了压力并进行了研究,以确定使用时任何衰老或降解问题。

高能质子辐照对GaN混合漏极的影响...

为了为 CERN 加速器隧道的新灯具提供耐辐射 LED 电源,需要对商用级功率晶体管在高水平粒子辐照下进行特性分析,因为这对半导体器件来说是一个恶劣的环境。这项工作描述了 24 GeV/ c 质子辐照对商用 GaN 混合漏极嵌入式栅极注入晶体管 (HD-GIT) 的影响,当时的剂量为 5.9 × 10 14 p/cm 2。漏极漏电流、阈值电压和 I ds − V ds 曲线的测量表明,在考虑的剂量之后,GaN HD-GIT 的电性能仅发生微小变化;例如,辐照后阈值电压平均增加约 11-13 mV。我们还对质子辐照引起的性能退化提出了物理解释;尤其是高电场下 2DEG 通道中的电子漂移速度似乎由于辐射引起的声子弛豫速率增加而降低。最后,提出了一种使用 GaN HD-GIT 进行电流控制的 AC/DC LED 电源,用于 CERN 隧道的新型灯具,满足辐射硬度和光质量方面的要求。

M.Tech学位课程和VLSI设计的课程和教学大纲

主题代码主题名称L-T-P CRORC 22101设备建模3-0-0 3模块1(13小时)半导体表面,理想的MOS结构,MOS设备,热平衡中的MOS设备,非理想的MOS:工作函数差异,氧化物中的电荷,氧化物,界面状态,界面状态,非理想的MOS,flate traptage thatbage,flattage thatbage thatbage thatbage thatbage thatbage thatbage thatbage thatbage thatbage coldection a MOS,电荷计算(计算),计算,计算,计算,计算,计算,计算,计算,计算,计算,计算,计算电压,MOS作为电容器(2个端子设备),三个端子MOS,对阈值电压的影响。模块2(10小时)MOSFET(增强和耗尽的MOSFET),活动性,对当前特征,当前特征,亚刺孔摇摆,界面状态对子阈值的影响对子阈值的影响,排水电导和跨导电,源偏置的影响,源偏置和身体偏置对阈值电压和设备操作。模块3(6小时)缩放,短通道和狭窄的通道效应 - 高场效应。模块4(5小时)MOS晶体管在动态操作中,大信号建模,低频率和高频的小信号模型。模块5(8小时)SOI概念,PD SOI,FD SOI及其特征,SOI MOSFET,多门SOI MOSFET的阈值电压,替代MOS结构。参考:1。E.H. Nicollian,J。R. Brews,《金属氧化物半导体 - 物理与技术》,John Wiley and Sons。 2。 Nandita Das Guptha,Amitava Das Guptha,半导体设备建模和技术,Prentice Hall印度3. Jean- Pierrie Colinge,硅启用技术:VLSI的材料,Kluwer学术出版商集团。 4。 Yannis Tsividis,MOS晶体管的操作和建模,牛津大学出版社。E.H. Nicollian,J。R. Brews,《金属氧化物半导体 - 物理与技术》,John Wiley and Sons。2。Nandita Das Guptha,Amitava Das Guptha,半导体设备建模和技术,Prentice Hall印度3.Jean- Pierrie Colinge,硅启用技术:VLSI的材料,Kluwer学术出版商集团。4。Yannis Tsividis,MOS晶体管的操作和建模,牛津大学出版社。5。M.S.Tyagi,《半导体材料和设备简介》,John Wiley&Sons,ISBN:9971-51-316-1。