机构名称:

¥ 6.0

上市时间是决定集成电路设计开发成本的关键因素。自动化部分设计过程的工具可以节省开发时间,因为本质上是跳过了这些部分。在本项目中,基于现有存储器设计,使用 Cadence SKILL 语言为此目的开发了一个只读存储器生成器。此设计是一个具有 12 位输入地址的 1.8 V 异步存储器。位线的数量直接对应于输出数据总线的宽度。生成器功能包括存储器原理图和布局生成、存储器重新编程、自动解码和布局后访问时间模拟,以及生成用于 Verilog 中解码模拟的功能模型。可以使用直接集成到 Cadence Virtuoso 菜单中图形用户界面单独运行这些功能。在正常条件下,创建的内存范围从 128 B 到 65.536 kB,访问时间从 4.2 ns 到 6.9 ns。角运行显示最多比原始值增加 78%。此外,生成的内存布局面积从 21397 µm2 到 829776 µm2。最大内存生成时间为 1 小时 31 分钟。

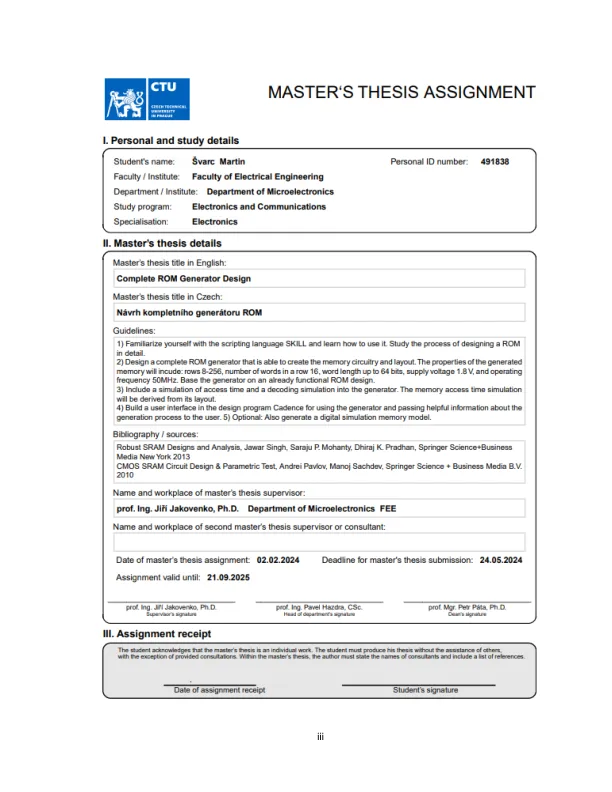

布拉格捷克理工大学电工技术...

主要关键词