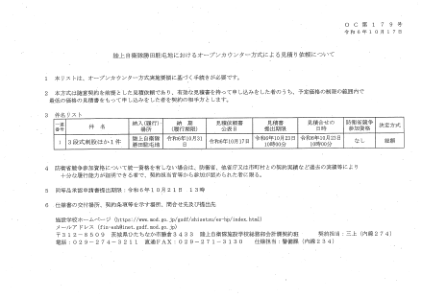

机构名称:

¥ 4.0

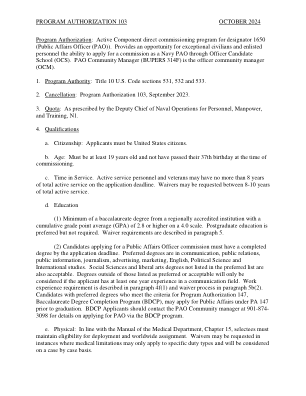

在本次会议中,我们将探讨 VLSI 设计和单元优化的前沿技术。在第一篇论文中,作者讨论了一种合成面积最优多行标准单元的最佳方法,集成了晶体管折叠、行分区和晶体管布局。第二篇论文介绍了 ATPlace2.5D,这是一种用于大规模 2.5D-IC 的分析热感知芯片布局框架。它平衡了线长和温度。在第三篇论文中,作者介绍了 3D SRAM 阵列的新方法:字线和位线折叠。这些设计显著减少了占用空间,提高了速度和能效。最后,第四篇论文提出了 MAXCell,这是一种使用任意时间 MaxSAT 的 PPA 导向标准单元布局优化框架,超越了线长优化研究。

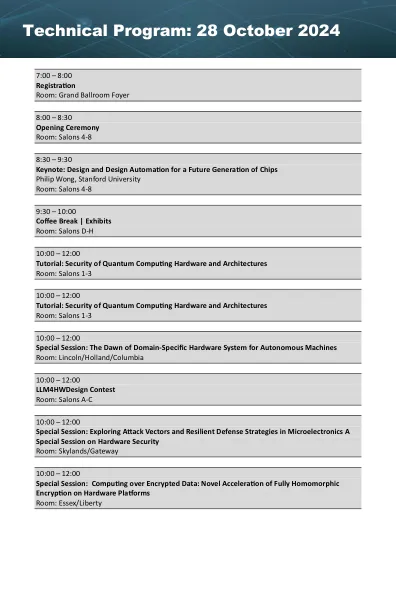

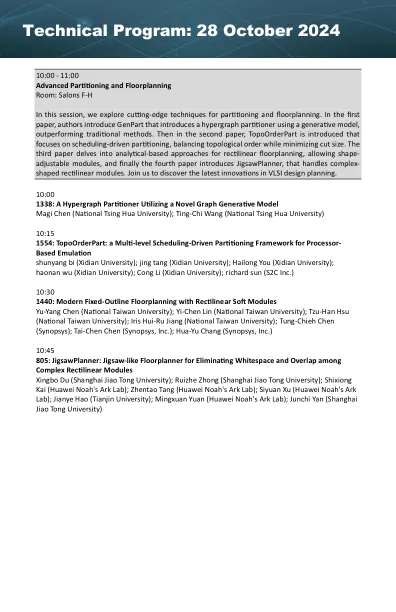

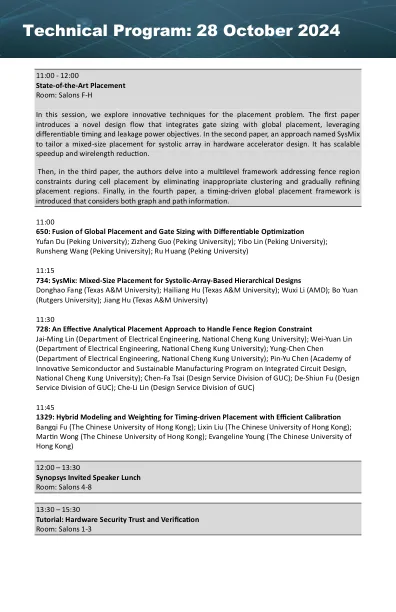

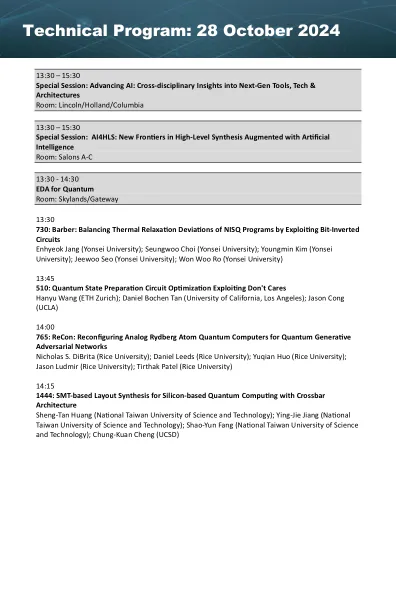

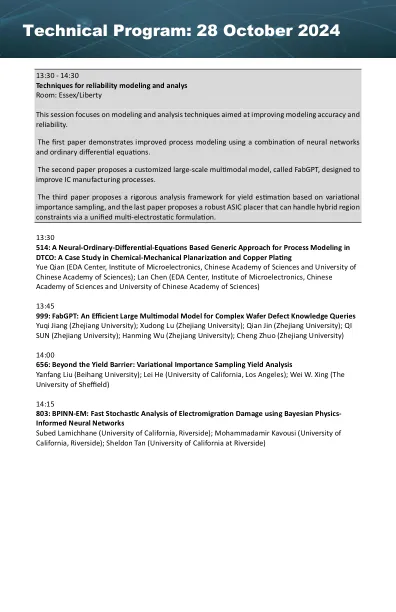

技术计划:2024 年 10 月 28 日