机构名称:

¥ 1.0

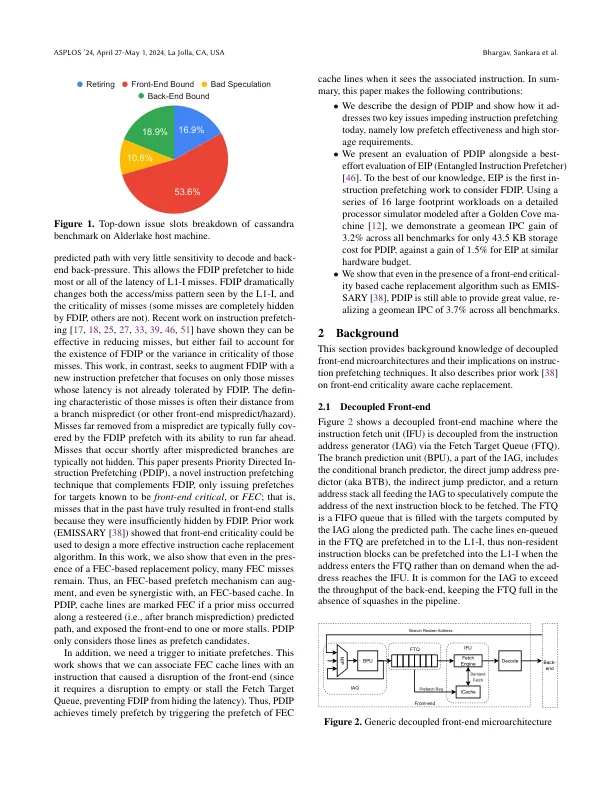

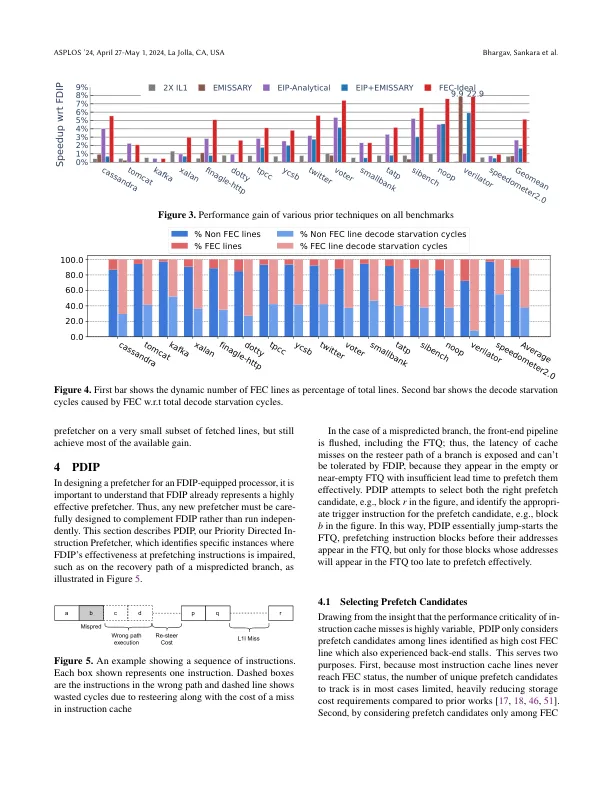

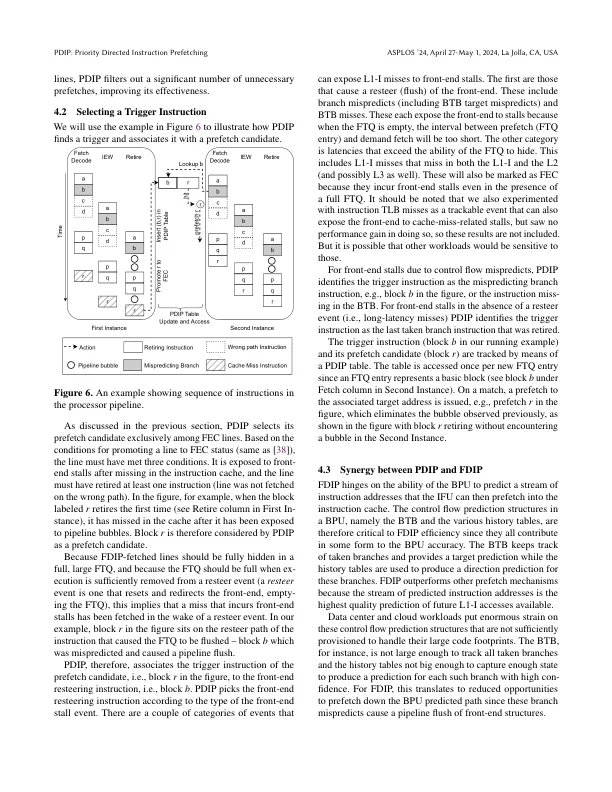

现代服务器工作负载具有较大的代码占用空间,由于指令缓存容量未命中,这些代码很容易出现前端瓶颈。即使现代处理器中实现了积极的提取定向指令预取 (FDIP),由于 I-Cache 未命中,仍然会出现严重的前端停顿。FDIP 可以容忍 BPU 预测路径上发生的大部分未命中,而不会导致停顿。然而,先前的指令预取工作并非设计用于 FDIP 处理器。它们的唯一目标是减少 I-Cache 未命中,而 FDIP 处理器则旨在容忍它们。设计与 FDIP 协同工作的指令预取器需要确定影响前端性能的缓存未命中比例(未被 FDIP 完全隐藏),并仅针对它们。在本文中,我们提出了优先级定向指令预取 (PDIP),这是一种新颖的指令预取技术,它通过仅针对 FDIP 遇到困难的目标发出预取来补充 FDIP——沿着导致前端停顿事件的重新引导路径。PDIP 识别这些目标并将它们与未来预取的触发器相关联。在 43.5KB 的预算下,PDIP 在重要的工作负载(例如 Cassandra)上实现了高达 5.1% 的 IPC 加速,并在 16 个基准测试中实现了 3.2% 的几何平均 IPC 加速。

PDIP:优先级定向指令预取 - UCSD CSE

主要关键词