机构名称:

¥ 1.0

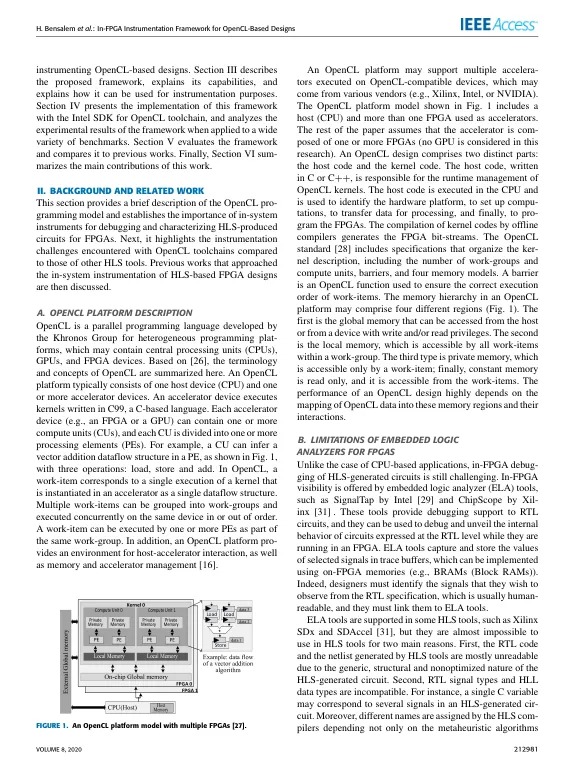

摘要通过使用开放的计算语言(OPENCL)提高了对高性能重新确定异质计算(HPRHC)系统的生产率。但是,在可编程的门阵列(FPGA)中,OpenCL编译器生成的硬件可能会导致严重的性能瓶颈解决方案。问题是由于生成的NetList细节杂乱无章的事实,使它们大部分不可读取,并且仅对设计师而言仅部分可见。本文提出了一种FPGA仪器方法和一个新的框架,用于提取基于OpenCL的设计的FPGA周期 - 准确的时间表演。结果清楚地表明,基于OPENCL的设计的选择执行模型在未正确实现时会强烈影响时间性能。我们的框架是在包含CPU和两个ARRIA10 FPGA的HPRHC平台上实现的,并通过各种具有不同复杂性的基准进行评估。在报告的基准测试后,一个插入仪器的平均逻辑开销是自适应查找表(ALUTS)总量的0.2%,而FPGA中总寄存器的0.1%。此资源利用率比最佳先前发表的作品中报告的资源低1.5至六倍。还可以通过插入多达50个乐器来评估框架的可伸缩性。实验结果表明,当插入50个仪器时,每工具的平均逻辑利用率为0.19%的Alut和0.17%的寄存器。

基于OpenCL的设计的FPGA仪器框架

主要关键词