机构名称:

¥ 1.0

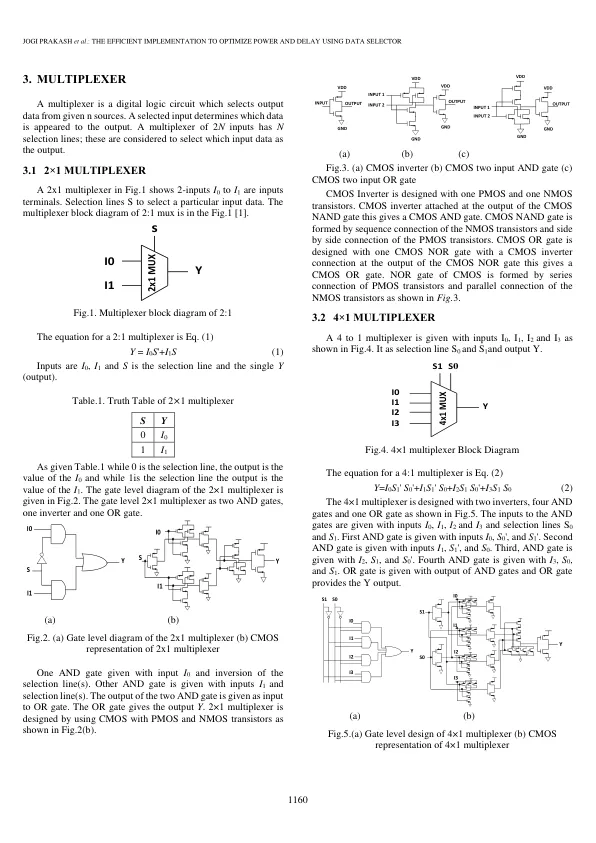

摘要 本文的目的是使用逻辑门和 CMOS 逻辑设计一个 16:1 多路复用器。在本研究中,我们研究了 16:1MUX 的延迟和功率调制。这表明 CMOS 技术处于领先地位,因为它使用的晶体管数量更少、电容更少、速度更快。在本研究中,我们进行了比较工作并得到了模拟结果,结果说明了 CMOS 逻辑设计的优越性,并且功耗和延迟非常低。使用 Synopsys 工具 HSPICE 在 32 nm BSIM 4 模型卡下对 PTM 模型的块状 CMOS 技术进行了模拟,并检查了不同电压下的结果。最小和最大延迟和功耗结果分别为 68.82ps、92.16ps 和 103.96µW、1471.4µW。我们在多路复用器中获得的总晶体管数量为 282,这是模拟的,我们使用名为 HSPICE 的高级工具获得了 MUX 的输出波形,它们在结果部分中表示出来。关键词:多路复用器、2×1 多路复用器、4×1 多路复用器、8×1 多路复用器、16×1 多路复用器、延迟、功耗

使用以下方法高效优化功耗和延迟

主要关键词