机构名称:

¥ 2.0

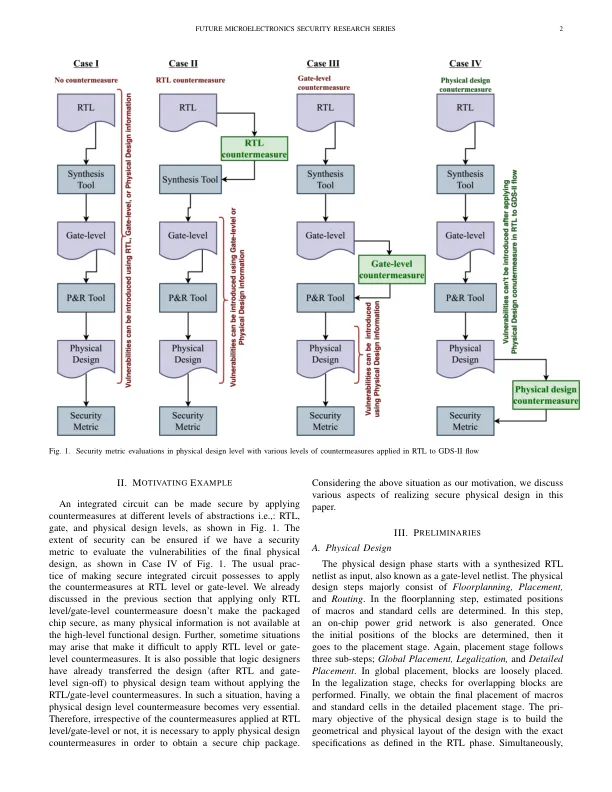

摘要 — 集成电路容易遭受多种攻击,包括信息泄露、旁道攻击、故障注入、恶意更改、逆向工程和盗版。大多数此类攻击都利用了单元和互连的物理布局和布线。已经提出了几种措施来处理高级功能设计和逻辑综合的安全问题。但是,为了确保端到端的可信 IC 设计流程,必须在物理设计流程中进行安全签核。本文提出了一种安全的物理设计路线图,以实现端到端的可信 IC 设计流程。本文还讨论了利用 AI/ML 在布局级别建立安全性。本文还讨论了获得安全物理设计的主要研究挑战。

安全物理设计 - 密码学 ePrint 存档 - IACR

主要关键词