机构名称:

¥ 2.0

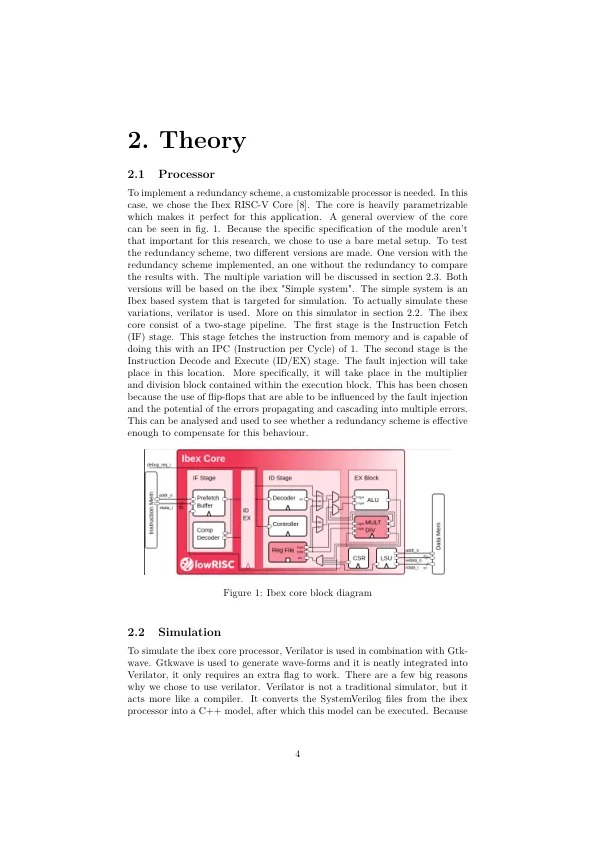

本文研究了三重模块冗余 (TMR) 实现对系统可靠性的影响。为此,对具有 RISC-V 架构的微处理器进行了模拟,分别采用了 TMR 实现和未采用 TMR 实现。在模拟中,注入了单事件瞬变 (SET) 和多事件瞬变 (MET)。此外,还模拟了采用 TMR 实现的晶体管故障。TMR 应用于处理器的 Multi/Div 块,故障将注入这些三重块的输入端。将使用注入故障数与传播故障数之比来比较采用和未采用 TMR 的系统的性能。当系统仅注入 SET 时,不采用 TMR 的系统的比例从 0.058 到 0.389,具体取决于发生 SET 的概率,而采用 TMR 的系统则根本不传播任何故障。如果注入 MET,则不带 TMR 的系统性能会更好,比率在 0.069 和 0.291 之间,而带 TMR 的系统比率在 0 和 0.036 之间。TMR 实施可显著降低错误传播的概率,但如果多事件瞬变击中多条类似的线路,它仍可能失败。为了解决这个问题,应该实施其他形式的冗余。

三模冗余可靠性分析

主要关键词