机构名称:

¥ 1.0

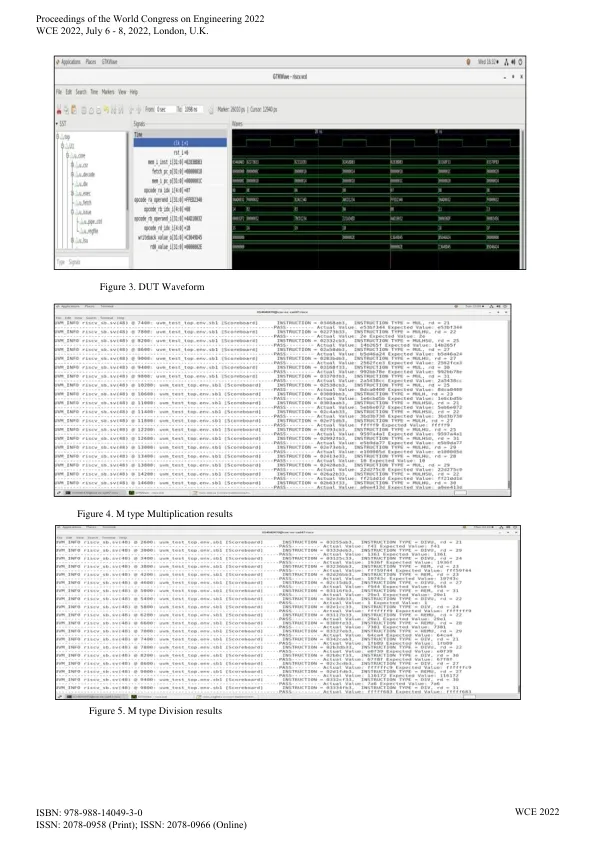

摘要 — RISC-V 处理器的开源架构为设计人员提供了灵活性,使他们能够为各种应用实现架构。然而,同样的优势也使验证过程变得困难,因为必须验证所有变体。拟议的项目将为扩展的 RISC V 架构创建一个验证环境。RISC-V 支持整数乘法和除法的“M”标准扩展以及控制和状态寄存器指令的“Zicsr”标准扩展。上述 ISA 类将使用基于 RV32I ISA 的 DUT 进行测试,并在 DUT 周围使用 UVM 环境来验证 M 和 Zicsr 功能。M 和 Zicsr 类型 ISA 经过验证,功能覆盖率为 95%。创建的 UVM 框架可以重复用于验证其他指令集架构。

超越 RV32I ISA 的 RISC-V 处理器验证