机构名称:

¥ 1.0

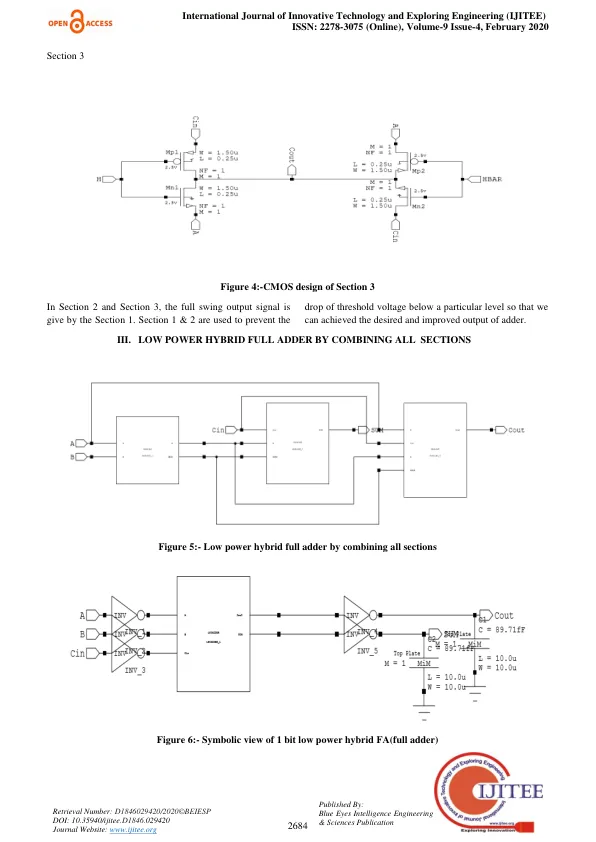

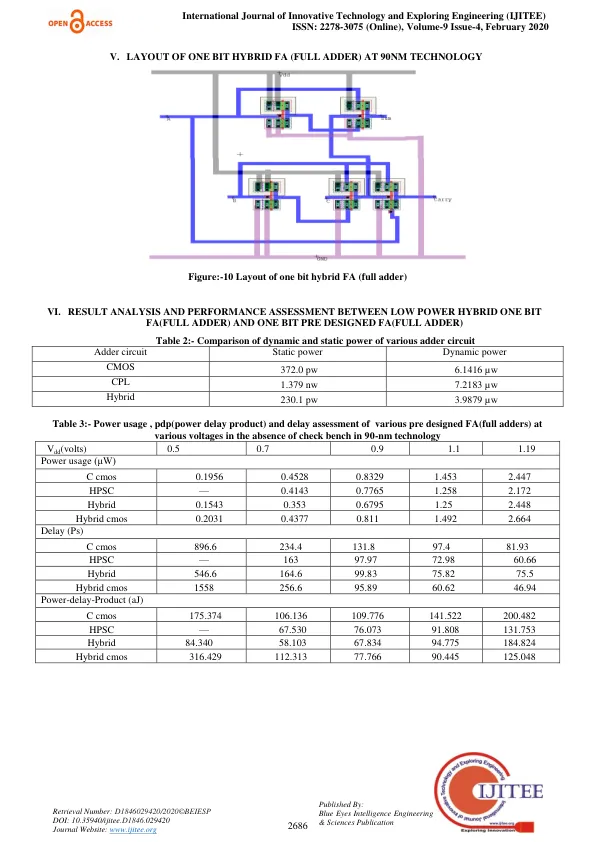

摘要:在电子处理系统中,二进制数的加法是一项基本运算。通过分析并与其他传统加法器进行比较,展示了一位低功耗混合全加器的性能改进。与其他传统全加器电路相比,1 位低功耗混合全加器被认为是提高电路速度的好方法。在该分析论文中,使用 EDA 工具实现了一位低功耗混合全加器,并使用通用 90nm CMOS 技术在 5 伏电压下进行了仿真分析,并在各种电压下与其他传统全加器进行了比较。为了将 1 位低功耗混合全加器与其他传统加法器在各种参数(例如静态和动态功耗、延迟和 pdp(功率延迟积))下的比较,考虑了 1 位低功耗混合全加器最适合各种低功耗应用。

适合低功耗应用的全加器