机构名称:

¥ 1.0

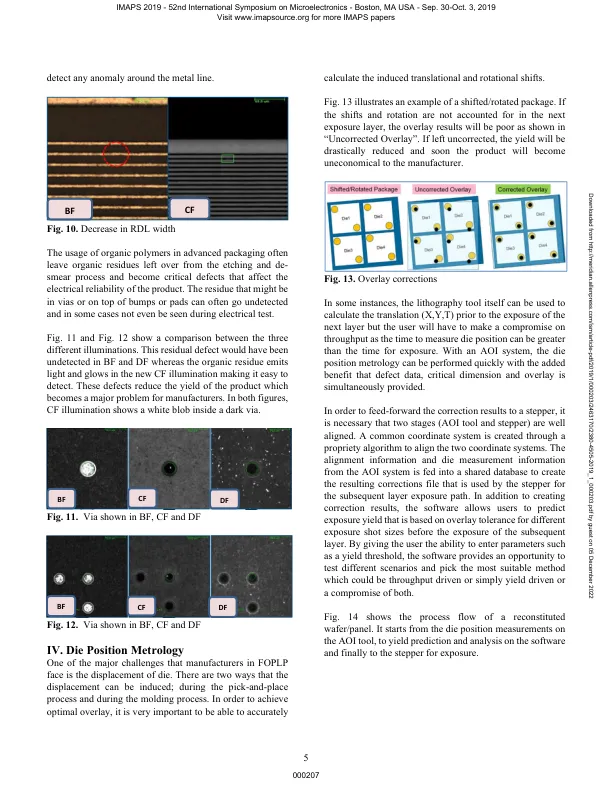

作为IC制造的最后一步,包装是封装芯片并提供最终表单I/O的互连的过程。对越来越高的I/O密度,缩小设备尺寸和较低成本的需求也适用于包装过程。为了实现这些目标,已经开发了各种技术,其中大多数是晶圆级包装(WLP)。与传统的包装过程不同,大多数I/O互连是在晶状体级别进行的,并使用重新分布层(RDL)进行。rdls是铜线和远处形成电气连接的层。取决于应用程序的市场,例如移动,内存或物联网(IoT),粉丝 - 外部晶圆级包装(FOWLP)提供了支持I/O密度要求和良好的RDL线/空间的最有希望的方法。此外,还开发了粉丝范围的面板级包装(FOPLP),以利用规模经济并优化底物利用率。在这项技术中,该过程中使用了矩形基板,而不是像晶圆那样的圆形底物。

与同时模具计量学的FOPLP自动化光学检查(AOI)

主要关键词