机构名称:

¥ 1.0

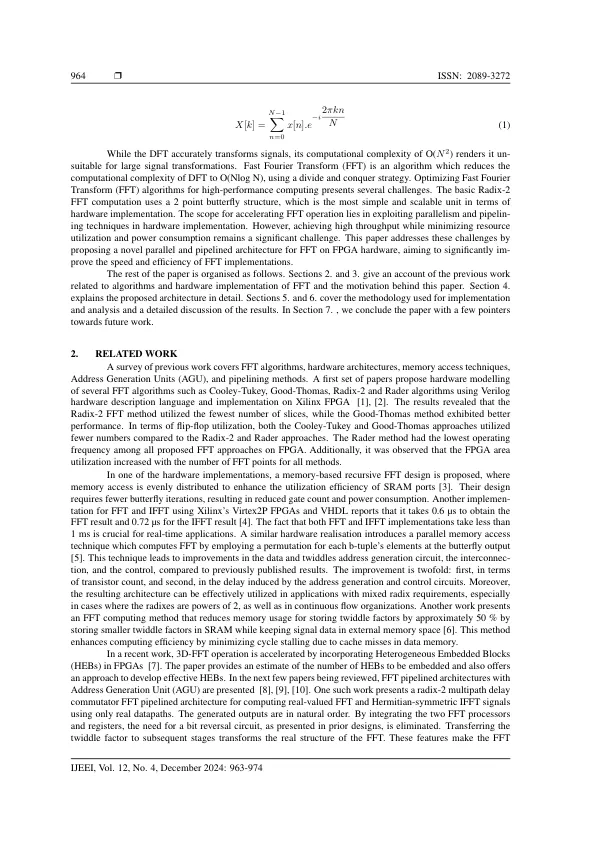

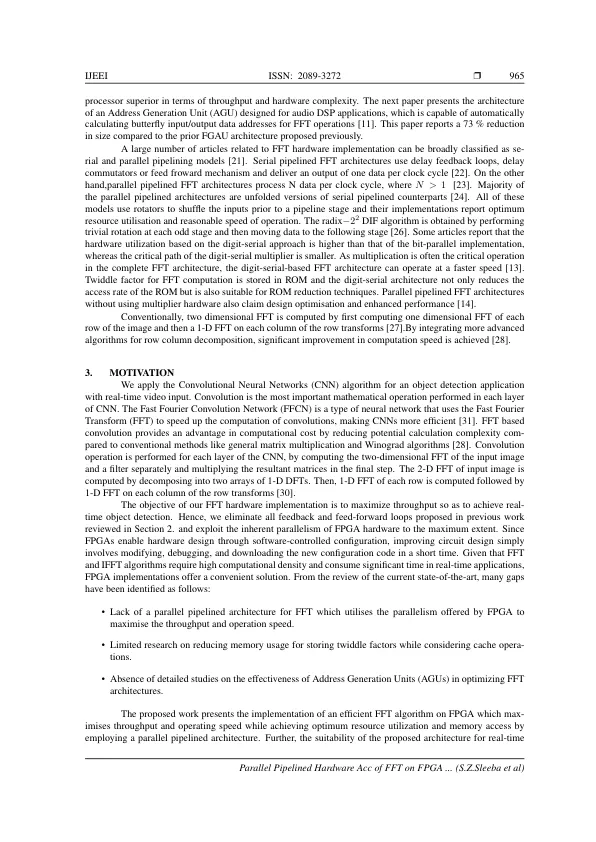

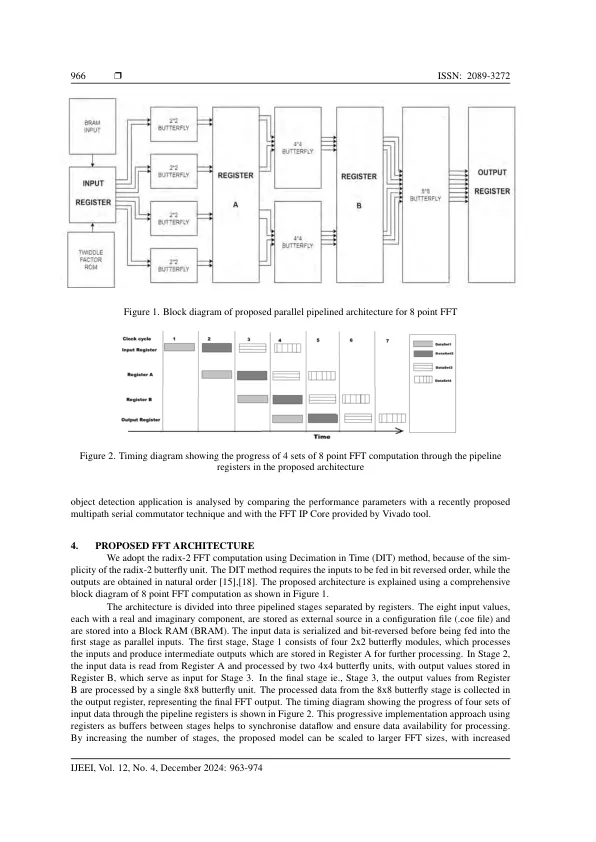

快速傅立叶变换(FFT)广泛用于数字信号处理应用中,尤其是用于使用CNN实时对象检测的卷积操作。本文提出了用于在FPGA上实现的Radix-2 FFT计算的有效的硬件档案,采用了蝴蝶单元的多个平行和管道阶段。所提出的架构利用块RAM存储输入和Twiddle因子值来计算转换。在Zync Ultrascale FPGA上合成了所提出的体系结构的硬件,并使用诸如关键路径延迟,吞吐量,设备利用率和功耗等参数评估其性能。发现在FFTOPS中测量的8点FFT所提出的平行管道结构的性能比非二叠体的AR插条高67%。性能比较与最新的并行管道管道方法证实了所提出的FFT体系结构达到的加速度。在论文中还介绍了拟议的硬件与与Vivado Design套件捆绑在一起的FFT IP核心的合成版本的全面比较。

FPGA上的快速傅立叶变换的平行管道硬件加速度

主要关键词