机构名称:

¥ 1.0

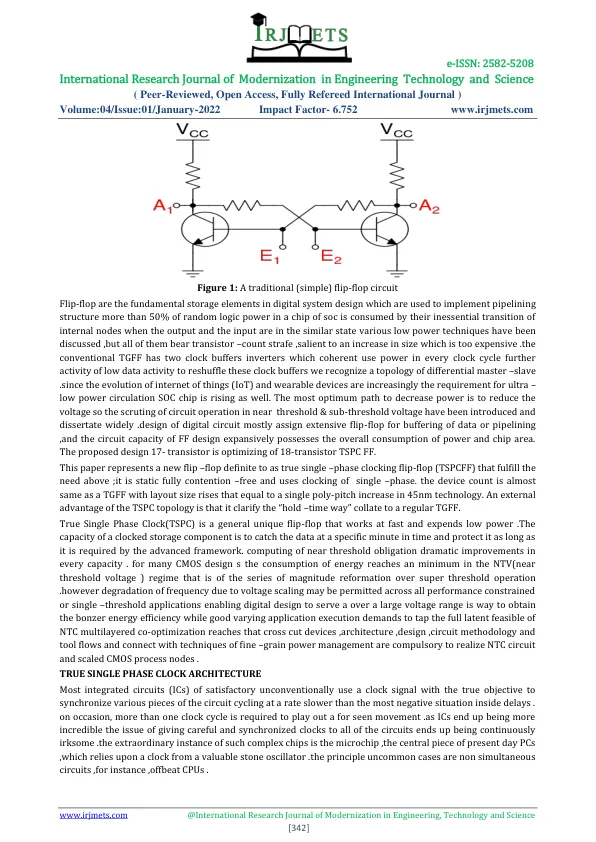

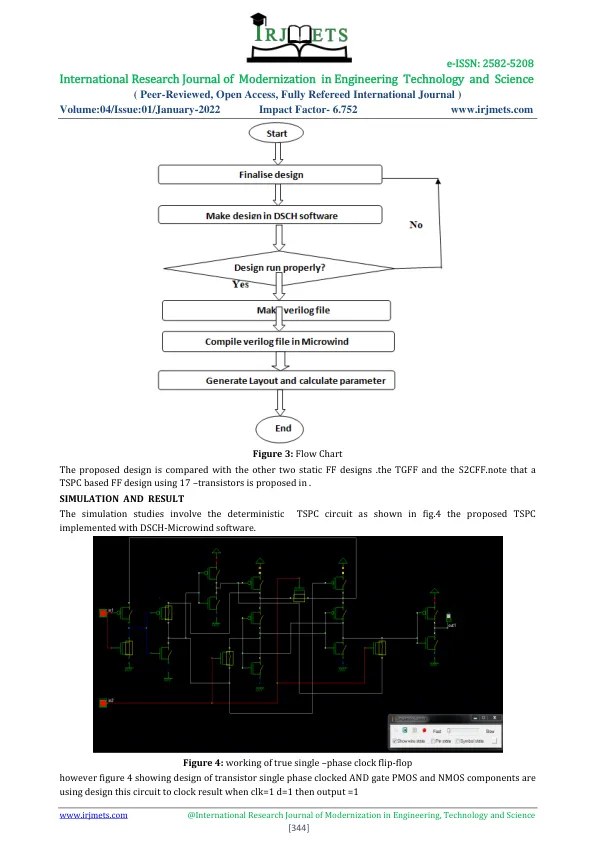

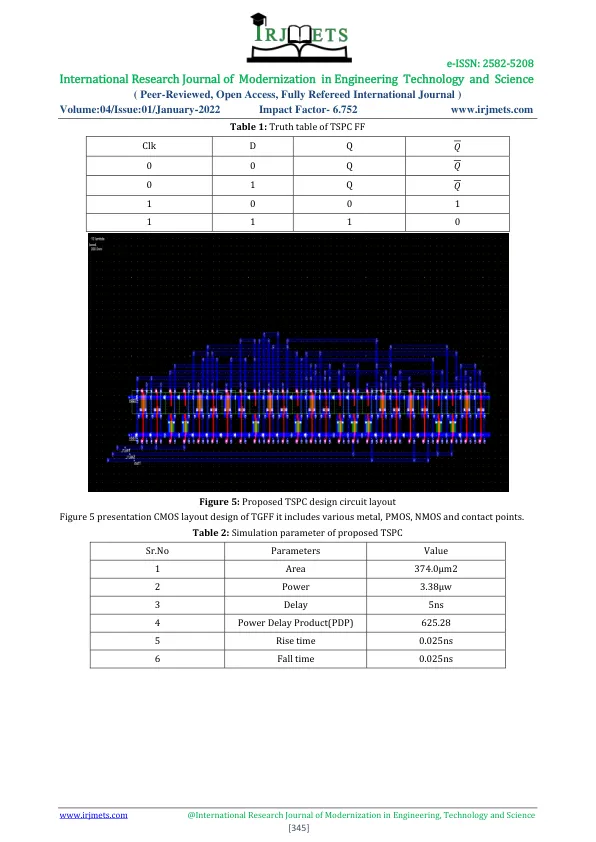

触发器(FF)是数字系统设计中大量使用的基本存储组件,涉及流水线结构和由 FF 构建的模块。FF 占总功耗的很大一部分,并且占数字系统的芯片面积很大。因此需要低功耗和小面积的 FF 设计。本文中低功耗 17 – 真单相时钟 (TSPC) 推理方法在高级计划中得到了广泛应用。提出了一种45 nm CMOS触发器。所提出的TSPC FF的逻辑结构为主从型,其中主级由静态CMOS逻辑形成,而从级由静态CMOS逻辑和互补传输晶体管逻辑的混合组合形成。所提出的TSPC FF电路是完全静态的,因为在操作期间没有内部节点处于浮动状态,这实际上防止了泄漏功耗。所提出的TSPC FF是通过在面积和功耗方面优化17晶体管逻辑结构减少触发器(LRFF)而设计的,但不影响FF的功能。在DSCH和MICROWIND工具中,使用gpdk 45 nm技术库以1v的电源电压vdd和500mhz的时钟频率实现和模拟了三个FF,即基于传输门的触发器(TGFF)、LRFF和所提出的TSPC FF。

相位时钟触发器设计与45

主要关键词